SDRAM Technology

SDRAM Technology. An introduction to the use of the technology in the high-reliability, spaceflight environment. Overview. Technology Background Heavy Ions Protons Loss of Functionality Radiation Signal Integrity Upset Predictions Total Ionizing Dose References

SDRAM Technology

E N D

Presentation Transcript

SDRAM Technology An introduction to the use of the technology in the high-reliability, spaceflight environment.

Overview • Technology Background • Heavy Ions • Protons • Loss of Functionality • Radiation • Signal Integrity • Upset Predictions • Total Ionizing Dose • References • Appendix - Some Additional Data

User Notes • This represents a sampling of information • Radiation data on each part type, revision, and lot may be radically different • Test data is only for modes tested; these are complex devices with many operating modes. • Examples of commands, structures, features, idiosyncrasies, may vary from device to devices. Examples are given for illustration purposes only.

Some SDRAM Features • Synchronous Timing • Signal generation much simpler than DRAM • Complex devices with state machines, pipelines, refresh modes, power states, etc. • Like DRAM, startup sequence required • Details available in data sheets

Control Signals Sampled Synchronously Block DiagramMicron, 64 Mbit 4 Banks Mode Register

Block DiagramMicron, 64 Mbit Control Signals Sampled Synchronously CKE CLK CS* WE* CAS* RAS* Mode Register

Control Signal Interpretation Function CS* RAS* CAS* WE* COMMAND INHIBIT H X X X NOP H X X X LOAD MODE REGISTER L L L L AUTO/SELF REFRESH L L L H PRECHARGE L L H L ACTIVE (SEL BANK/ROW) L L H H WRITE L H L L READ L H L H BURST TERMINATE L H H L

Load Mode Register CommandAddress Used As Operation Code A2:A0 Burst Length A3 Burst Type {Sequential, Interleaved} A6:A4 CAS Latency A8:A7 Operation Mode A9 Write Burst Mode A11:A10 Reserved

Load Mode Register CommandExamination of Some Fields - Burst Length BURST LENGTH A2 A1 A0 M3=0 M3=1 0 0 0 1 1 0 0 1 2 2 0 1 0 4 4 0 1 1 8 8 1 0 0 RESERVEDRESERVED 1 0 1 RESERVED RESERVED 1 1 0 RESERVED RESERVED 1 1 1 FULL PAGE RESERVED

Load Mode Register CommandExamination of Some Fields - CAS Latency A6 A5 A4 CAS LATENCY 0 0 0 RESERVED 0 0 1 RESERVED 0 1 0 2 0 1 1 3 1 0 0 RESERVED 1 0 1 RESERVED 1 1 0 RESERVED 1 1 1 RESERVED

Load Mode Register CommandExamination of Some Fields - Op Mode A8 A7 Operation Mode 0 0 Standard Operation 0 1 RESERVED 1 0 RESERVED 1 1 RESERVED

Self Refresh Load Mode Reg Auto Refresh Idle Idle Power Down Read/ Write Power On Pre- charge State Diagram, Simplified [3]Hitachi 256M SDRAM

Sample Current Consumption by Mode @ VCC = 3.3V [3] Operating Mode Current (mA) Auto Refresh 4.3 Write/Read 13 Self Refresh 2.2 Idle 1.1

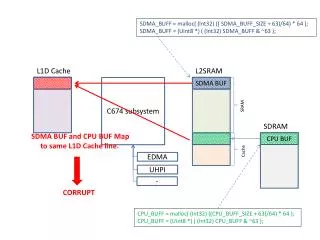

Mode Register and Device StateSpecial Considerations • Mode Register likely SEU Soft • Test data supports this • RESERVED states in Mode Register • May be able to load invalid state • May require power cycle • May result in damage to device • Toggling N/C Pins • May require power cycle to recover • May result in damage to device • Poor Signal Integrity or Power/Ground Noise • May upset Mode Register: put into a RESERVED state

Power-On Self-Test (POST) • “Since the ultimate value of a DRAM is a highly reliable memory function, a special control circuit has been incorporated to ‘map out’ defective or non-operational cells from the whole memory section by a proper distribution of built-in redundant cells. It appears that the ‘mapping out’ process takes place during the power-up.” [2] • Discussions with Micron indicated that they did not have this feature. • Reliability and radiation effects on devices may significantly differ.

Heavy Ion SEUs: 16 Mbit [4] Micron MT48LC1M16A1TG-10SIT 1Mx16 This device was rotated along the short axis of the device to emulate higher LET.

KM44V1600B Cross-section (cm2/bit) LET (MeV-cm2/mg) Heavy Ion SEUs, 64 Mbit (Samsung [2])

SEE Event SEL Cross-section (cm2/device) KM44S32030B LET (MeV-cm2/mg) Heavy Ion SEUs, 128 Mbit Samsung [2]

Heavy Ion SEUs, 256 Mbit [2] • Samsung • Multiple bit upsets seen • LETTH is around 1 MeV-cm2/mg • Add Figure 5 • Hitachi • Multiple bit upsets seen • LETTH is around 1 MeV-cm2/mg • Add Figure 8

Heavy Ion SEL: 16 Mbit [4] Micron MT48LC1M16A1TG-10SIT 1Mx16 No SELs were observed below 11.5 MeV-cm2/mg Chlorine at normal incidence.

Heavy Ion SEL Data (1 of 2) • 64 Mbit Samsung • No SEL at LET = 50 MeV-cm2/mg [1] • No SEL at LET = 65 MeV-cm2/mg [2] • 128 Mbit Samsung • No SEL at LET = 82 MeV-cm2/mg [1] • SEL at LET = 15 MeV-cm2/mg; device destroyed [2] • Rev. A: SEL at ~ 55 MeV-cm2/mg [3] • Rev. B: SEL at ~ 5 MeV-cm2/mg [3]

Heavy Ion SEL Data (2 of 2) • 256 MBit Samsung • No SEL at LET = 30 MeV-cm2/mg [2] • Latched at LET = 36 MeV-cm2/mg [2] • Current > 200 mA • 256 MBit IBM [3] • SEL at LET ~ 30 MeV-cm2/mg • 256 MBit Hitachi [3] • No SEL at LET = 61 MeV-cm2/mg, 100 °C • 256 MBit Hyundai [3] • No SEL at LET = 12 MeV-cm2/mg

Heavy Ion: Stuck Bits • Reference [1] reports 30 stuck bits on one 128 Mb device, after exposure to a large fluence. Fewer stuck bits observed after being annealed at room temperature, unbiased for one week. • Reference [2] reports stuck bits for the 256M Samsung devices. The small number of stuck bits annealed within a few weeks in an unbiased condition.

10-6 10-7 10-8 10-9 10-10 SEU Cross-section (cm2/device) KM44S64230A KM44S32030B Proton Energy (MeV) Proton SEUs128, 256 MBit Samsung [2] Note: No multiple-bit upsets, SEFI, or latchup detected.

Total DoseSamsung 64 and 128 Mbit • Dose rates from 13 to 140 krad(Si)/s • 64 Mbit fully functional up to 22 krad(Si) • 128 Mbit fully functional up to 17 krad(Si)

Loss of Functionalityand otherUnusual Events Radiation Signal Integrity

“Large Event” - Samsung [1] Most or all bits “wrong” were seen a few times for the 128 Mbit Samsung device; it was not seen for the 64 Mbit Samsung SDRAM.

Loss of Functionality - Early Data • 256M Samsung [2] • “Often, ‘reset’ (power cycle) is needed to recover from SEFI conditions.” [2] • Large multiple bit errors (> 100 bits) making an oval patch in the memory • Multiple-bit errors over many consecutive address locations • Events above may have an increase of about 10 mA in supply current. • 256 Hitachi [2] • Also seen. Add figure. • Anomalous Currents • Ranged from 0.5 to 145 mA [3]

Loss of Functionality [3]Hyundai 256M (Auto Refresh Operation) 10-3 10-4 10-5 10-6 10-7 Cross-section (cm2/device) LET (MeV-cm2/mg)

Bias Current (mA) Xe Fluence (particles/cm2) Loss of Functionality [3]Hyundai 256M: Bias Current Variation

Loss of FunctionalityAdditional Issues • Refreshing MODE Register • Will restore functionality in some cases • But not all! • Different ways of operating SDRAM can result in different affects from radiation. See Reference [3] for details.

Loss of FunctionalityProtons [3] • Hyundai, Hitachi 256M devices • SEFI not detected at 197 MeV

Loss of Functionality - A SampleSee Ref. 3 for Detailed Data Self-Refresh Operation: Power Cycle Required LET HIT256M HYND256M SAM128M SAM256M 4.1 - N/A - N/A 12 X N/A X X 28 X X X X - No problem N/A Data Not Available X Power Cycle Required

Commercial Designs • Employing Error Detection and Correction • Parity • SEC/DED • Protect again loss of an entire chip

References [1] "SDRAM Space Radiation Effects Measurements and Analysis," B.G. Henson, P.T. McDonald, and W.J. Stapor, 1999 IEEE Radiation Effects Data Workshop, Norfolk, Virginia, 1999. [2] "SEE Sensitivity Determination of High-Density DRAMs with Limited-Range Heavy Ions," R. Koga, S.H. Crain, P. Yu, and K.B. Crawford, 2000 IEEE Radiation Effects Data Workshop. [3] "Permanent Single Event Functional Interrupts (SEFIs) in 128- and 256-megabit Synchronous Dynamic Random Access Memories (SDRAMs)," R. Koga, P. Yu, K.B. Crawford, S.H. Crain, and V.T. Tran, 2001 IEEE Radiation Effects Data Workshop. [4] "SEE Measurement at Brookhaven National Laboratory for the SDRAMs,"Leif Scheick, December 1999, Unpublished

References [5] "IBM moves to protect DRAM from cosmic invaders,” Anthony Cataldo, EE Times, http://www.edtn.com/news/june11/061198topstory.html [6] " Phasor — The Next Generation Cosmic Ray Fighter!,” Don Swietek, MicroNews, Second Quarter 1999, Vol. 5, No. 2, IBM, http://www-3.ibm.com/chips/micronews/vol5_no2/swietek.html