Introduction to DDR SDRAM

Introduction to DDR SDRAM. Bill Gervasi Technology Analyst wmgervasi@attbi.com. Topics to Cover. The SDRAM Roadmap Transitioning from SDR to DDR DDR-I 400 Overview Market overview. SDRAM Evolution. 5400MB/s. Mainstream Memories. DDR667. 4300MB/s. DDR533. 3200MB/s. DDR400. 2700MB/s.

Introduction to DDR SDRAM

E N D

Presentation Transcript

Introduction toDDR SDRAM Bill Gervasi Technology Analyst wmgervasi@attbi.com

Topics to Cover • The SDRAM Roadmap • Transitioning from SDR to DDR • DDR-I 400 Overview • Market overview

SDRAM Evolution 5400MB/s MainstreamMemories DDR667 4300MB/s DDR533 3200MB/s DDR400 2700MB/s “DDR II” DDR333 2100MB/s DDR400? 3200MB/s DDR266 1600MB/s DDR200 1100MB/s “DDR I” PC133 Simple,incrementalsteps “SDR”

Key to System Evolution • Never over-design! • Implement just enough new features to achieve incremental improvements • Use low cost high volume infrastructure • Processes • Packages • Printed circuit boards

From SDR to DDR Prefetch2 Prefetch2 DifferentialClocks Signaling& Power WriteLatency DataStrobe

Prefetch • Today’s SDRAM architectures assume an inexpensive DRAM core timing • DDR I (DDR200, DDR266, and DDR333) prefetches 2 data bits: increase performance without increasing core timing costs • DDR II (DDR400, DDR533, DDR667) prefetches 4 bits internally, but keeps DDR double pumped I/O • DDR-I 400 is a prefetch-2 architecture

Prefetch Depth CK data SDR: Prefetch 1 READ Core access time DDR-I: Prefetch 2 DDR-II: Prefetch 4 Costs $$$ Column cycle time Essentially free Costs $$$

Prefetch Impact on Cost SDRAM Family Pre-fetch DataRate CycleTime High Yield = Affordable 1 100 10 ns SDR 1 133 7.5 ns 2 200 10 ns DDR-I 2 266 7.5 ns Starts to get REAL EXPENSIVE! 2 333 6 ns 2 400 5 ns DDR-II 4 400 10 ns 4 533 7.5 ns Comparable to DDR266 in cost

DDR Data Timing • Data valid on rising & falling edges… “Double Data Rate” • Source Synchronous; Data Strobe “DQS” travels with data

From SDR to DDR Prefetch2 DifferentialClocks DifferentialClocks Signaling& Power WriteLatency DataStrobe

DDR Clocks • Differential clocks on adjacent traces • Timing is relative to crosspoint • Helps ensure 50% duty cycle

Single Ended Clock VREF CK Clock high time Clock low time Normal balanced signal VREF CK Clock high time Clock low time Mismatched Rise & Fall signal Error!

Differential Clock CK CK Clockhigh time Clock low time Normal balanced signal CK CK Clock high time Clock low time Mismatched Rise & Fall signal Significantly reduced symmetry error

From SDR to DDR Prefetch2 DifferentialClocks Signaling& Power Signaling& Power WriteLatency DataStrobe

DDR Signaling • SSTL_2 low voltage swing inputs • 2.5V I/O with 1.25V reference voltage • Low voltage swing with termination • Rail to rail if unterminated

Power = CV2f%# Factors: • Capacitance (C) • Voltage (V) • Frequency (f) • Duty cycle (%) • Power states(# circuits in use) Keys to lowpower design: Reduce C and V Match f to demand Minimize duty cycle Utilize power states

Power: SDR DDR-I DDR-II DDR533@ 1.8V DDR266@ 2.5V PC-133@ 3.3V

From SDR to DDR Prefetch2 DifferentialClocks Signaling& Power WriteLatency DataStrobe DataStrobe

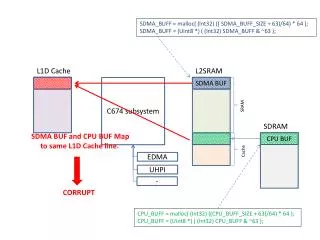

Emphasis on “Matched” DDR SDRAM CONTROLLER • DM/DQS loading identical to DQ • Route as independent 8bit buses DQ/DQS VREF VREF DM VREF VREF Disable

64 = 8 x 8 • 64bit bus is 8 sync’ed 8bit buses • Allows external “copper” flexibility • 8 buses resync upon entry to FIFO x16 DDRSDRAM x16 DDRSDRAM x16 DDRSDRAM x16 DDRSDRAM Copperfromcontrollerto SDRAMs 8 DQ1 DM1 DQS 8 DQ1 DM1 DQS 8 DQ1 DM1 DQS InsideController 8bit Buffer 8bit Buffer Sync toControllerclock 64bit Memory Controller Internal FIFO

From SDR to DDR Prefetch2 DifferentialClocks Signaling& Power WriteLatency WriteLatency DataStrobe

Write Latency • SDR had to keep inputs powered all the time • Adding Write Latency to DDR allowed inputs to be powered off between commands • Flexible timing differences on data and address paths

3200MB/s DDR400 2700MB/s DDR333 DDR400? 3200MB/s DDR-I vs DDR-II @ 400 “DDR II” “DDR I”

DDR-I 400 Summary • DDR-I is hard to design to 400 MHz data rate • Lower yields • No JEDEC standard • Prefetch-2, 2.5V signals, TSOP packages, write latency 1 • DDR-II makes it a lot easier • JEDEC standards & focus • Prefetch-4, 1.8V signals, differential strobe • On-die termination, BGA packages, write latency > 1 • Same plane referencing • Few suppliers supporting DDR-I 400 market

DDR-I 400 Conclusion • The JEDEC roadmap represents the industry focus for mainstream products • DDR-I tops out at 333 MHz data rate • DDR-II starts at 400 MHz data rate • This DOES NOT mean that DDR-I at 400 MHz data rate will not ship in volume • It DOES mean that there will be price premiums for this speed bin

Market Outlook • DDR-I • DDR333 is the mainstream product for 2003 • DDR-I 400 will be the premium market • DDR-II • DDR-II designs under way now • DDR-II 400 & 533 will sample in 2003 • DDR-II ramp begins in 2004

Summary • DDR has many improvements over SDR • Prefetch, differential clock, low voltage, data strobe, write latency • DDR-I 400 likely to stay a profitable niche • DDR-II volume products for 400 & 533 ramp in 2004