CSCE 491: Capstone Computer System Project

CSCE 491: Capstone Computer System Project . Instructor: Jason D. Bakos. Introduction. Goals of this course: Use engineering principals to design and build a computer system Work in teams Written and oral communication skills Official course outcomes:

CSCE 491: Capstone Computer System Project

E N D

Presentation Transcript

CSCE 491: Capstone Computer System Project Instructor: Jason D. Bakos

Introduction • Goals of this course: • Use engineering principals to design and build a computer system • Work in teams • Written and oral communication skills • Official course outcomes: • Refine a topic, formulate an approach, and solve computer engineering problems to achieve a project goal; • Manage time and efforts as a team to achieve a project goal; • Pursue an independent project under time and design constraints; • Develop effective written and oral skills to communicate among team members as well as with outsiders in a real-world styled environment; • Design a system, consisting of both hardware and software components, using the techniques, skills, and tools of modern computer engineering practice.

Platform • Xilinx University Program (XUP) board from Digilent

491’s Place • CSCE 313: Embedded Systems Lab • Design flow: Xilinx EDK • Design embedded system using the XUP board • Involves hardware design and writing systems software for PPC405/MicroBlaze/PicoBlaze CPUs • CSCE 611: Conceptual Modeling Tools for CAD • Design flow: Mentor Graphics FPGA Advantage • Use hardware description language to design microprocessor • CSCE 613: Fundamentals of VLSI Chip Design • Design flow: Cadence IC-Tools, Synopsys synthesis • Semiconductors, ASIC design-for-manufacturing • CSCE 491: Capstone Computer System Project • Design flow: Xilinx/MATLAB System Generator for DSP • Design a “novel” hardware device

Project: Active Noise Cancelation PC case, rear projection TV, car console S quiet zone noise anti-noise error mic reference mic F(x) adaptive algorithm student design

Course Organization • 12 students, 4 teams of 3 • Approximate timeline: • Lectures for first week • 2 tutorials • Getting started with System Generator for DSP • Audio filtering tutorial for whole design flow • Design work • Find information • Testing • Each group will present their progress twice during the semester • Final report, presentation, and demonstration at the end of the semester

System Generator for DSP • Xilinx add-on for MATLAB Simulink • Block-diagram interface for designing digital systems, esp. DSP systems • Has special design tokens that perform FPGA-specific functions • VHDL generation, synthesis, place-and-route • Resource estimation

Design Components • Toolbox that includes parameterizable primitives, including: • adder/substractor, multiplier • accumulator • shift register, LFSR • concat, slice, convert • counter • delay • DSP48 • RAM • constant • boolean logic, mux, shift • Microblaze/Picoblaze • LogicCore components • black box • M-code blocks • MATLAB code can be converted to VHDL

Simulation • Works with Simulink’s simulation system • Scopes • Spectrum analyzers • WAVE-IN, WAVE-OUT • Debugger • Waveform interface • Modelsim interface • To-Workspace

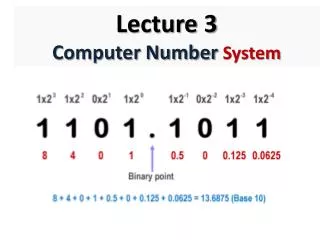

I/O, Clocking, and Data Types • I/O is handled using gateway in/out blocks • No explicit clock signals • “Sample rate” defined for • Gateway blocks • M-code blocks • All primitives that have memory • System Generator only supports • boolean (single bit) • signed and unsigned fixed-point • example: • signed 6/4 fixed bit value: 1 0 . 1 0 0 1 negate to become 0 1 . 0 1 1 1 => - (20 + 2-2 + 2-3 + 2-4) => -1.4375

AC97 • We only need access to the audio interface of the board • 2 input channels (amp/non-amp), 2 output channels (amp/non-amp) • The audio jacks are connected directly to a National Instruments LM4550 chip • Performs A/D, D/A, power amplication • Sample rates from 4 – 48 KHz • 18 bit • Uses the AC97 (Audio Code) digital interface protocol • SDATA_IN, SDATA_OUT, BIT_CLK, SYNC • Operates at 24.576 MHz

Wrapper • Xilinx has designed a wrapper design for the XUP board for use with System Generator • Includes AC97 controller • Provides a simple interface to the user design: • audio_left_in, audio_right_in, audio_left_out, audio_right_out • the FPGA clock is connected to the 24 MHz AC97 clock (can be downsampled) • Disadvantage of wrapper • Name of user design must match that assumed by wrapper (“audio”) • Interface of user design must match that assumed by wrapper • Cannot interface to anything else on the board • Xilinx’s wrapper is not open source

M-code Block • Implemented as a MATLAB function • Function inputs act as ports or block instance parameters • Supports a subset of the MATLAB language • assignment statement • if/else/elseif statement • switch statement • add/sub/mult • divide by power of 2 • logical and relational operators • “Bit twiddling” • ex: xl_slice(), xl_concat(), xl_and(), xl_lsh(), xl_force(), … • Internal signals • Must use xfix() to convert parameters and scalers (both double) to fixed-point • Memory • persistant, xl_state() • register, addressible memory, or “line of registers” (vector)