Performance-oriented Peephole Optimisation of Balsa Dual-Rail Circuits

140 likes | 308 Vues

Performance-oriented Peephole Optimisation of Balsa Dual-Rail Circuits. Luis Tarazona and Doug Edwards Advanced Processor Technologies Group School of Computer Science. Syntax-directed compilation. Used in Tangram and Balsa

Performance-oriented Peephole Optimisation of Balsa Dual-Rail Circuits

E N D

Presentation Transcript

Performance-oriented Peephole Optimisation of Balsa Dual-Rail Circuits Luis Tarazona and Doug Edwards Advanced Processor Technologies Group School of Computer Science

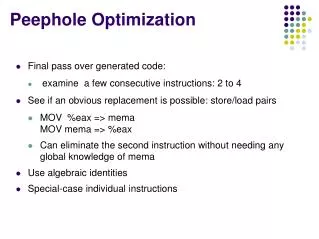

Syntax-directed compilation • Used in Tangram and Balsa • One-to-one mapping of each language construct into a network of handshake components (HCs) • Benefits: • Transparency and flexibility to the designer • Drawback: medium-low performance • Solutions to this have been proposed using: • Control resynthesis • Peephole optimisation

Related work • Tangram and Balsa compilers perform some peephole optimisations as a post processing step • T. Chelcea has proposed resynthesis and peephole optimisations for Balsa, targeting a burst-mode back-end • Plana et al. have proposed some optimised HCs for Balsa targeting single rail and dual-rail back-ends Main interest of this work is on dual-rail back-ends due to its potential immunity to process variability.

The optimisations • Eliminating redundant FalseVariable components • New Concurrent RTZ Fetch component • Conditional parallel/sequencer component: ParSeq

Eliminating redundant FVs • Targets active input control • Single access, single read-port FalseVariable or eagerFalseVariable HCs i -> then CMD end

Eliminating redundant FVs - Example • Latency and area reduction • Preserves external behaviour a, b -> then o <- a + b end

Concurrent RTZ Fetch Wires-only dual-rail Fetch and its STG

Concurrent RTZ Fetch New concurrent RTZ Fetch and its STG

The ParSeq • Acts conditionally as a Concur (parallel) or as a Sequencer HC • Few opportunities to apply it in the design examples available • Perhaps caused by its inexistence at that time? • Interesting increase in performance, though.

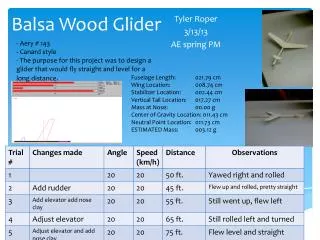

Simulation Results Pre-layout, transistor-level simulations, 180nm technology

Conclusions and Future Work Future work: • To incorporate the optimisations into the Balsa design flow • ParSeq as a construct or as a peephole optimisation? • To evaluate other peephole and HCs optimisations currently under study

Thank you very much! Questions? Acknowledgement • Thanks to Luis Plana, Andrew, Charlie and Will for their suggestions and comments. • This work and PhD are supported by EPSCR and UoM School of Computer Science scholarships.