Adding SG-DMA core and programming

Adding SG-DMA core and programming. m 5151117 Yumiko Kimezawa. Scatter-Gather DMA controller. : Data flow : Control signal. Ethernet PHY. JTAG UART. LED. Graphic LCD. SG-DMA Controller. Filtered Data Memory. TSE MAC. LED Controller. Graphic LCD Controller.

Adding SG-DMA core and programming

E N D

Presentation Transcript

RPS Adding SG-DMA core and programming m5151117 Yumiko Kimezawa

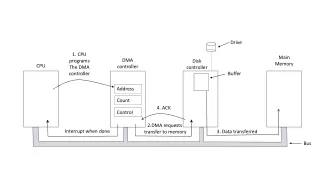

Scatter-Gather DMA controller RPS : Data flow : Control signal Ethernet PHY JTAG UART LED Graphic LCD SG-DMA Controller Filtered Data Memory TSE MAC LED Controller Graphic LCD Controller ECG Data Rom Slave CPU Slave CPU Memory Avalon Bus Master CPU TX SGDMA Timer Master CPU Memory FIR Filter Shared Memory Timer Ethernet Module PPD Module Master Module

SG-DMA for Filtered Data Memto Shared MemConfig. RPS CPU Memory 32Byte SG-DMA core Control & Status Reg. Descriptor Table • Source addr • Destination addr • Next desc pointer • Bytes to transfer • Desc controller command DMA Write Block descriptor_read Descriptor Processor Block status descriptor_write status DMA Write Block command Filtered Data memory Shared Memory

How the DMA descriptors are processed RPS • Building and updating descriptor listI stored in in an on-chip memory • 2. Software writes the address of the first descriptor to the next_descriptor_pointerreg. to 1On the next clock cycle following the assertion of the RUN bitThe core sets the BUSY bit in the status reg. to 1 • 5. The descriptor processor block receives… Memory 32Byte Descriptor Table • Source addr • Destination addr • Next desc pointer • Bytes to transfer • Desc controller

How the DMA descriptors are processed RPS • Building and updating descriptor listI stored in in an on-chip memory • 2. Software writes the address of the first descriptor to the next_descriptor_pointerreg. to 1On the next clock cycle following the assertion of the RUN bitThe core sets the BUSY bit in the status reg. to 1 • 5. The descriptor processor block receives… • Reference design or application note are not found • It takes much time to program software Memory 32Byte Descriptor Table • Source addr • Destination addr • Next desc pointer • Bytes to transfer • Desc controller

Future Work RPS • Tasks by next week • Implementation of Scatter-Gather DMA • Finish writing background of master thesis