BEE3 Update

During the January 2008 RAMP Retreat, participants from Microsoft Research, Celestica, and other partners shared updates on the BEE3 project. Key topics included the status of subsystems, initial gateware, and performance benchmarks. The bring-up status indicated progress with the MicroBlaze and communication channels, although challenges remained with the DDR2 controller. The schedule outlined completed phases such as schematic entry and thermal modeling, with board qualification still underway. This collaboration aims to advance system engineering and FPGA application expertise for research and industry.

BEE3 Update

E N D

Presentation Transcript

BEE3 Update Chuck Thacker John Davis Microsoft Research Chen Chang BWRC/BEECube 16 January 2008 January 2008 RAMP Retreat

Outline • BEE3 board properties • BEE3 gateware • BEE3 schedule January 2008 RAMP Retreat

Lab January 2008 RAMP Retreat

John explains a tricky point to Chuck January 2008 RAMP Retreat

BEE3 January 2008 RAMP Retreat

BEE3 January 2008 RAMP Retreat

Bandwidths (per-FPGA) • Memory • 400 MT/s * 9B/T * 2 channels: 7.2 GB/s • Ring • 500 MT/s * 9 B/T * 2 channels: 9.0 GB/s • QSH • 400 MT/s * 10 B/T: 4 GB/s • Ethernet • 125 MB/s • CX4 • 1.25 GB/s * 2 directions * 2 channels: 5GB/s • PCI Express • Same as CX4 January 2008 RAMP Retreat

Initial Gateware • Mostly things required for production testing and board characterization: • Signal connectivity checks • Some are AC coupled, must test at speed • QSH tested with a crossover card • Temperature and power supply monitoring • DDR-2 Controller • Useful in other designs • CX4 and PCI Express for at-speed tests • Xilinx and others have lots of IP (alas, it either doesn’t work very well, or is proprietary). January 2008 RAMP Retreat

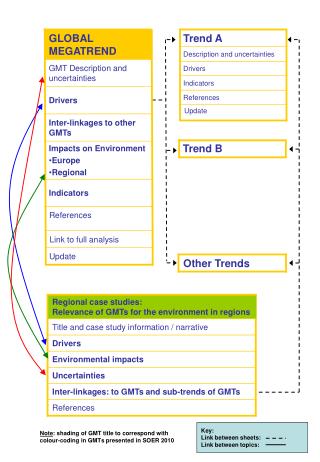

Project Participants and Roles • Microsoft Research (Silicon Valley) • Funds, manages system engineering, does some gateware • Celestica (Ottawa and Shanghai) • Did main board engineering, prototype fabrication • Microsoft has a very deep relationship with Celestica • BEECube • Builds and delivers functioning systems • Function Engineering (Palo Alto) • Did thermal and mechanical engineering • Xilinx (San Jose) • Provides FPGAs for academic machines • Provides FPGA application expertise • Ramp Group (BWRC) • Control board, basic software • Ramp Community • Uses the systems for research • Expanding to industrial users (e.g., us) January 2008 RAMP Retreat

Bring-up Status • Most subsystems work: • Brought up a MicroBlaze on day 3 of bring-up • Ring wiring • 10 Gbit channels • Works, but requires respin to relocate MGTs • GB Ethernet • PCI Express January 2008 RAMP Retreat

Bring-up Status (2) • DDR2 controller doesn’t work (yet) • Largest piece of “new” IP • Works flawlessly in post-route simulation • Timing complete at 200 MHz. • Problems: • Design is complex • Six Verilog modules, including a 36-bit RISC • Design turnaround is ½ hour (i.e., tools suck). • Simulator is slow • Board testing uses ChipScope • Which doesn’t replace a ‘scope • Very difficult to probe January 2008 RAMP Retreat

Schedule • Generate Specification – Done • Schematic Entry – Done • Board Layout – Done • Thermal modeling, heat sink design – Done • Chassis design -- Done • Signal Integrity – Done • Board Qualification – In progress • Board Respin -- TBD • Prototypes: Spring • Production: Start Summer ‘08 January 2008 RAMP Retreat