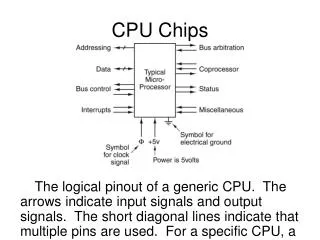

CPU Chips

CPU Chips. The logical pinout of a generic CPU. The arrows indicate input signals and output signals. The short diagonal lines indicate that multiple pins are used. For a specific CPU, a number will be given to tell how many. Computer Buses (1). A computer system with multiple buses.

CPU Chips

E N D

Presentation Transcript

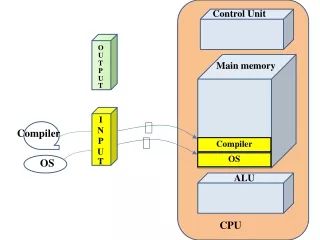

CPU Chips The logical pinout of a generic CPU. The arrows indicate input signals and output signals. The short diagonal lines indicate that multiple pins are used. For a specific CPU, a number will be given to tell how many.

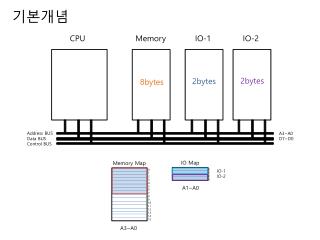

Computer Buses (1) A computer system with multiple buses.

Buses • Links device(s) • Internal to CPU or External • This chapter is external buses • Multiple buses in computer • Some buses run of other buses • Can be used for • Control • Data • Address

Buses (cont) • External buses are well defined to allow interconnect (Bus protocol) • Examples • ISA • EISA • USB • FireWire

Buses • Three types • Masters Active initiate transfer – bus drivers • Slaves Passive receive data – bus receiver • Both – both transceiver May not match CPU multiplexer decoder

Computer Buses (2) Examples of bus masters and slaves.

Bus Width Growth of an Address bus over time.

Bus Width • Tradeoffs • Speed • Cost • Capabilities • Compatibility ISA – 20 address lines – 1 MB EISA - 32 Address lines - 4 GB

Speed • Synchronous buses • Increase clock speed • Increase width Problems Compatibility Bus skew Multiplexing

Bus Clocking (1) Read timing on a synchronous bus.

Bus Clocking (2) Specification of some critical times.

Asynchronous Buses Operation of an asynchronous bus.

Asynchronous Buses • Not tied to clock • Uses new technology • More control lines • Not as many chips are available

Bus Arbitration (1) (a) A centralized one-level bus arbiter using daisy chaining. (b) The same arbiter, but with two levels.

Arbitration • Only bus masters are concerned • Two types • Centralized – some logic external to device requesting access • Decentralized – logic in each device that could request access

Bus Arbitration (2) Decentralized bus arbitration.

Bus Operations (1) A block transfer.

Bus Operations • Single word or block transfer • Read modify write cycle • Interrupts • Time critical priorities

Bus Operations (2) Use of the 8259A interrupt controller.

The Pentium 4 The Pentium 4 physical pinout.

Pentium 4 Logical pinout of the Pentium 4. Names in upper case are the official Intel names for individual signals. Names in mixed case are groups of related signals or signal descriptions.

Pentium 4 • 478 pins • One corner is missing pins for alignment • On board bus arbitration • All transfers are on 8 byte boundary with 8 bytes at a time • Controls power use to reduce heat

Pipelining on the Pentium 4’s Memory Bus Pipelining requests on the Pentium 4’s memory bus.

Pentium 4 Pipeline • Bus Arbitration • Request phase • Error-reporting phase • Snoop phase • Response phase • Data pahse • Each phase uses different bus signals

The UltraSPARC III (1) The UltraSPARC III CPU chip.

UltraSPARC III • RISC computer – 64 bit • Designed for multiprocessor systems • 6 internal pipelines – up to 14 stages • 1368 Land Grid array package • Up to 8TB of memory • Address memory thru UDB II (UltraSPARC Data Buffer II)

The UltraSPARC III (2) The main features of the core of an UltraSPARC III system.

The 8051 (1) Physical pinout of the 8051.

The 8051 (2) Logical pinout of 8051 Logical pinout of the 8051.

8051 • Embedded system processor • 40 pin package • 8 bit data bus • 4 or 8 KB of internal ROM

The ISA Bus The PC/AT bus has two components, the original PC part and the new part.

ISA • ISA Industry Standard Architecture • Runs at 8.33 MHz • PC 62 line bus + 36 Lines – ISA • EISA (Extended ISA) 32 bit

Bandwidth Calculations • 1024X768 screen with true color • Requirement for moving video is 30 fps • = 67.5 MB/sec of data for video only • Because screen must be read/generated, actual requirement = 135MB minimum • EISA has a maximum of 33.3 MB/sec

PCI • Original PCI 33 mhz with 32 bit bus = 133 MB/sec • PCI 2.0 66 mhz with 64 bit bus = 528 MB • Old PCI was 5.0 volts, new = 3.3 volts • APG added to offload video load from PCI • AGP 3.0 (8X) is 2.1GB • Master now call initiator • Slave now called target

The PCI Bus (1) Architecture of an early Pentium system. The thicker buses have more bandwidth than the thinner ones but the figure is not to scale.

The PCI Bus (2) The bus structure of a modern Pentium 4.

PCI Bus Arbitration The PCI bus uses a centralized bus arbiter.

PCI Bus Signals(1) Mandatory PCI bus signals.

PCI Bus Signals(2) Optional PCI bus signals.

PCI Bus Transactions Examples of 32-bit PCI bus transactions. The first three cycles are used for a read operation, then an idle cycle, and then three cycles for a write operation.

PCI Express A typical PCI Express system.

PCI Express Protocol Stack (a) The PCI Express protocol stack. (b) The format of a packet.

The Universal Serial Bus The USB root hub sends out frames every 1.00 ms.

USB • For slower devices • No switches to set • Do not open case • Power from cable • 127 devices from Cable • Support real-time • No reboot necesssary • Inexpensive

USB • 1.0 runs at 1.5 mbps • 1.1 runs at 12 Mbps • 2.0 runs at 480 Mbps • 4 wires 2 for data, power and ground • Time-sliced • No interrupts

USB • 4 types of frames • Control • Isochronous • Bulk • Interrupt Frame consists of packets data token handshake special

PIO Chips An 8255A PIO chip.

Address Decoding (1) Location of the EPROM, RAM, and PIO in our 64 KB address space.

Address Decoding (2) Full address decoding.