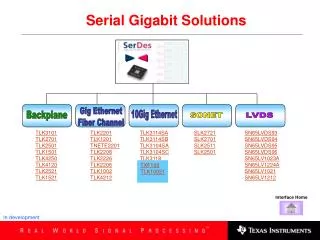

Serial Gigabit Solutions

Gig Ethernet Fiber Channel. 10Gig Ethernet. Backplane. SONET. LVDS. Interface Home. Serial Gigabit Solutions. TLK3101 TLK2701 TLK2501 TLK1501 TLK4250 TLK4120 TLK2521 TLK1521. TLK2201 TLK1201 TNETE2201 TLK2208 TLK2226 TLK2206 TLK1002 TLK4212. TLK3114SA TLK3114SB TLK3104SA

Serial Gigabit Solutions

E N D

Presentation Transcript

Gig Ethernet Fiber Channel 10Gig Ethernet Backplane SONET LVDS Interface Home Serial Gigabit Solutions TLK3101 TLK2701 TLK2501 TLK1501 TLK4250 TLK4120 TLK2521 TLK1521 TLK2201 TLK1201 TNETE2201 TLK2208 TLK2226 TLK2206 TLK1002 TLK4212 TLK3114SA TLK3114SB TLK3104SA TLK3104SC TLK3118 SLK2721 SLK2701 SLK2511 SLK2501 SN65LVDS93 SN65LVDS94 SN65LVDS95 SN65LVDS96 SN65LV1023A SN65LV1224A SN65LV1021 SN65LV1212 TXF100 TLK10021 In development

PRBS P-S 8b/10b Encoder 16-bit LVTTL PLL Clock PRBS Verification Clock Recovery 8b/10b Decoder 16-bit LVTTL S-P LOS Backplane SERDES Architecture Back to SerDes Summary

Single Channel Multi-Gigabit TransceiversProviding the lowest power in the industry at the highest data rates Power • Single Channel Transceiver Family • Common 16:1 Serializer/ De-Serializer • LVTTL parallel side interface • CML serial side interface* • LOS Detection • Industrial temperature qualified (except TLK2711JR) • Common Pin-Out for upgrade-ability • Evaluations Modules Available • Built-in testability features • On board PRBS generation and verification • Internal Loop Back TLK3101 2.5 – 3.125 Gbps 450 mW TLK2711 1.6– 2.7 Gbps 390 mW TLK2711JR 1.6– 2.7 Gbps 390 mW TLK2701 1.6– 2.7 Gbps 390 mW TLK2501 1.6 – 2.5 Gbps 360 mW TLK1501 0.6 – 1.5 Gbps 250 mW In Production Back to SerDes Summary *TLK2711 has VML driver with internal termination on Rx and TLK3101 has a VML driver with internal termination resistors

Single Channel 18 bit Multi-Gigabit TransceiversProviding the lowest power in the industry at the highest data rates Power • Single Channel Transceiver Family • 18:1 Serializer/ De-Serializer • 1.0 -2.5 Gbps Serial Data Rate (TLK2521) • .5 -1.3 Gbps Serial Data Rate (TLK1521) • LVTTL parallel side interface • VML serial side interface • Selectable signal Preemphasis on serial output • Lock indicator • Fast Synch mode • Equalization for long link lengths • Industrial temperature qualified TLK2521 1.0 – 2.5 Gbps < 540 mW TLK1521 .5 – 1.24 Gbps < 540 mW • TI advantages over competition • Lower Power • Built in Equalization • Proven core technology • Lower overall cost of implementation In Production Back to SerDes Summary

19 mm 1.0 mm 1.8 mm Multi Channel Multi-Gigabit TransceiversProviding the lowest power in the industry at the highest data rates Power • Four Channel Transceiver Family • Four single channel devices in one package • Each channel functionally equal to TLK2521 or TLK1521 • Common 18:1 Serializer/De-Serializer per channel • LVTTL parallel side interface • VML driver • Equalization for long link lengths • Industrial temperature qualified • 19x19mm, 289-Pin BGA 1.0mm ball pitch • Evaluations Modules Available • Built-in testability features • Internal Loop Back TLK4250 1 – 2.5 Gbps < 540 mW/ch TLK4120 0.5 – 1.24 Gbps < 500 mW/ch Pitch: 1.0mm Package height: 2mm (max) Footprint: 368.6mm2 (max) In Production Back to SerDes Summary Samples Now

Single Channel Gig Ethernet SERDES ArchitectureTLK1201 / TLK2201 PRBS 10-bits or 5-bits (DDR) P-S PLL Clock Clock Recovery PRBS Verification 10-bits or 5-bits (DDR) S-P and Comma Detect LOS Back to SerDes Summary

Single Channel Gigabit Ethernet TransceiversProviding the lowest power in the industry at the highest data rates • Gigabit Ethernet Transceiver Family • Offering both industry supported pin out in the TNETE2201B and out of the box performance in the TLK2201 • Common 10:1 Serializer/ De-Serializer interface • LVTTL parallel side interface • Differential PECL compatible serial interface • JTAG support (TLK2201/1201) • Selectable 10 bit or 5 bit parallel interface (TLK2201/1201) • TLK2201 I Temp version available • Built-in testability features (TLKX201) • On board PRBS generation and verification • Internal Loop Back Power TLK2201Ajr 1.0 – 1.6 Gbps 200 mW TLK2201B 1.0 – 1.6 Gbps 200 mW TLK2201AI I-temp 1.2 – 1.6 Gbps 200 mW TLK1201A 0.6 - 1.25 Gbps 150 mW TNETE2201B 1.25 Gbps 600 mW In Production Back to SerDes Summary

Multi-Channel Gig Ethernet SERDES ArchitectureTLK2208 Note: Single Channel Diagram PRBS 10-bits or 5-bits (DDR) FIFO P-S 8b/10b Encoder PLL Clock CTC Clock Recovery PRBS Verification 10-bits or 5-bits (DDR) FIFO 8b/10b Decoder S-P

19 mm 1.0 mm 1.8 mm TLK2208 Eight Channel Gigabit Ethernet TransceiverProviding the lowest power in the industry at the highest data rates Power • Octal Gigabit Ethernet Transceiver • 8 Channel Fibre Channel and Gigabit Ethernet (IEEE802.3z) synchronizable Transceiver • VML high speed I/Os with no external components • Selectable parallel interface modes • Multiplexed channel DDR Clock interface • Nibble-wide DDR clocking interface • Selectable 8b/10b encode/decode • JTAG support • Source Synchronous timing on inputs from MAC • 19x19mm, 289-Pin BGA 1.0mm ball pitch • Built-in testability features • Pin Compatible with PMC’s PM8352 TLK2208A 1.0 – 1.3 Gbps < 1W Pitch: 1.0mm Package height: 2mm (max) Footprint: 368.6mm2 (max) In Production Next

Multiplexed Mode Channel A, B (10-bits) A B C D E F G H MAC ASIC FPGA Channel C, D (10-bits) TX Channel E, F (10-bits) Channel G, H (10-bits) TLK2208 Transmit Timing Diagram A B C D E F G H Channel A, B (10-bits) Channel C, D (10-bits) - On falling edge of TCLKx channels A, C, E and G read - On rising edge of TCLKx channels B, D, F and H read Channel E, F (10-bits) RX Channel G, H (10-bits) Nibble Wide Mode Channel A (5-bits) A B C D E F G H MAC ASIC FPGA Channel B (5-bits) Channel C (5-bits) Channel D (5-bits) TX Channel E (5-bits) Channel F (5-bits) Channel G (5-bits) Channel H (5-bits) TLK2208 Channel A (5-bits) A B C D E F G H Channel B (5-bits) Channel C (5-bits) Channel D (5-bits) Transmit Timing Diagram RX Channel E (5-bits) Channel F (5-bits) - On falling edge of TCLKx channels least sign. nibble read - On rising edge of TCLKx channels most sign. nibble read Channel G (5-bits) Channel H (5-bits) TLK2208 Eight Channel Gigabit Ethernet TransceiverMultiplexed Mode and Nibble Wide Mode Next

TLK2208 Eight Channel Gigabit Ethernet TransceiverProviding the lowest power in the industry at the highest data rates Application Back to SerDes Summary

19 mm 1.0 mm 1.8 mm TLK2206 Four Channel SERDESSix ChannelGigabit Ethernet & Transceiver Power • Six Channel 1Gb EthernetTransceivers • 6 Channel Fibre Channel and/or Gigabit Ethernet (IEEE802.3z) synchronizable Transceiver • Selectable TBI or RTBI interface • Independent speed selection by channel • Selectable 8b/10b encode/decode • JTAG support • Low Jitter VML high speed I/Os with no external components • 19x19mm, 289-Pin BGA 1.0mm ball pitch • Compatible with PMC PM8373 • Built-in testability features • On board PRBS generation and verification • Internal Loop Back TLK2206 1- 1.3 Gbps < 1W Pitch: 1.0mm Package height: 2mm (max) Footprint: 368.6mm2 (max) Samples Now Back to SerDes Summary

19 mm 1.0 mm 1.8 mm TLK2226 Six Channel Gigabit Ethernet TransceiverProviding the lowest power in the industry at the highest data rates Power • Hex Gigabit Ethernet Transceiver • 6 Channel Gigabit Ethernet (IEEE802.3z) synchronizable Transceiver • VML high speed I/Os with no external components • Selectable parallel interface modes • RTBI compliant • RGMII Compliant • Selectable 8b/10b encode/decode • JTAG and MDIO supported • Source centered timing on inputs from MAC • 19x19mm, 289-Pin BGA 1.0mm ball pitch • Built-in testability features • Internal series termination on HTSL outputs TLK2226 1.0 – 1.3 Gbps < 1W Pitch: 1.0mm Package height: 2mm (max) Footprint: 368.6mm2 (max) Samples 3Q04 Back to SerDes Summary

TLK1002 Dual Gigabit Ethernet Signal Conditioner Power • Dual Gigabit Ethernet Signal Conditioner • TLK1002 - Two Channel 1GbE and 1GFC Signal cleaner • TLK4202 - Two Channel 1FC to 4GFC Signal cleaner • VML high speed I/Os with no external components • High input jitter tolerance (.75 UI) • 1.8 v supply voltage • 200mV p-p differential input sensitivity • 1800mV p-p differential output voltage swing • 4 x 4 mm, 24–Lead QFN package 0.5mm ball pitch • Built-in loop back function • <350mw power dissipation TLK1002 1.0 – 1.3 Gbps < 350 mw TLK4202 1.0 – 4.25 Gbps < 350 mw Packaging Package Type: 24 lead QFN Pitch: .5mm Package height: 1mm (max) Footprint: 17.22mm2 (max) Samples Now Samples 4Q04 Next

TLK1002 Dual Gigabit Ethernet Signal Conditioner Samples Feb 2004 Back to SerDes Summary

TLK4212 Dual Mux Buffer Power • Dual Mux Buffer • Multi-Rate Operation From 1.0 Gb/s Up To • 4.25 Gb/s • Selectable Loopback • Selectable Self-Adapting Input Equalization • Selectable Output Pre-Emphasis • On-Chip 100 : Differential Input Termination • On-Chip 2 u 50 : Output Back-Termination • Low Jitter CML Data Inputs And Outputs • Single +1.8-V Supply • Low Power Consumption • I2C Interface • Compatible to MAX3783 • Available in 7mm by 7mm 48 Pin TQFP • or 7mm by 7mm 48 Pin QFN Packages TLK4212 1.0 – 4.25 Gbps < 350 mw Samples 3Q04 Back to SerDes Summary

PRBS FIFO 8/10-bit SSTL/HSTL P-S 8b/10b Encoder PLL Clock CTC Clock Recovery Only on TLK3114SA & TLK3124SA PRBS Verification FIFO 8b/10b Decoder 8/10-bit SSTL/HSTL S-P 10 Gig Ethernet SERDES ArchitectureTLK31x4SA Back to SerDes Summary

TLK3114SB 2.5 - 3.125 Gbps/Chv 650mW/Ch TLK3114SC 2.5 - 3.125 Gbps/Ch 650mW/Ch Multi Channel Gigabit TransceiversProviding the lowest power in the industry at the highest data rates Power • Multi Channel Gigabit Transceiver Family • Four Channel, 3.125 Gbps per channel transceivers • Low power consumption < 185mW per Channel (TLK3124SA) • TLK3114SC: LVPECL serial side i/f w/SSTL_2 or HSTL parallel I/O with 802.3ae spec compliant features 10 Gigabit Ethernet • TLK3114SB: Pin Compatible with TLK3114SA with improved jitter tolerance, more sensitive front end receiver, and fixed TLK3114SA errata. • TLK3104SC: LVPECL serial side i/f w/LVDS 622Mhz parallel I/O DWDM Backplane • Selectable Independent Channels or Channel Sync Operation • Flow through pin out with 289 Ball PBGA package • JTAG Support TLK3104SC 3.0 - 3.125 Gbps/Ch 650 mW/Ch In Production Next

TLK3104SA TLK3114SC TLK3104SA TLK3114SA Multi Channel Gigabit TransceiversTLK31x4 Migration path • IEEE 802.3ae Compliant • <438mW/Ch @ 3.125Gbps • Pin to pin compatible with TLK3104SA • Clock Tolerance Compensation with Column add/drop • Comma detect on both negative and positive commas • XAUI A/, /K, and /R Code Generation and Stripping • Remote and Local Fault Reporting • Repeater mode • End of package error detection and reporting • Equalizer for improved ISI rejection • Clause 45 MDIO Registers supported • IEEE 802.3ae D2.0 Compliant • <650mW/Ch @ 3.125 Gbps • 8/10 bit SSTL2/HSTL parallel I/O • LVPECL compatible Serial I/O • Channel synch on/off • Selectable 8b/10b • Programmable pre-emphasis • JTAG • On-Chip Serial termination • 289 PBGA package + Next Note: TLK3104SC has same features as TLK3104SA, but has 4 bit LVDS interface and 8/10b non-bypassable

Standard interfaces to ASIC: XGMII or LVDS Ultra High Speed Back plane up to 34 inches 10 Gigabit Switch ASIC TLK31x4 TLK31x4 Switch ASIC 10 Gigabit TLK31x4 TLK31x4 10 Gigabit TLK31x4 TLK31x4 2.5 Gigabit 10 Gigabit 2.5 Gigabit TLK31x4 TLK31x4 Example: 40 Gigabit Concentrator Back to SerDes Summary

Multi Channel Gigabit TransceiversProviding the lowest power in the industry at the highest data rates • Multi Channel Gigabit Transceiver Family • Four Channel, 3.2 Gbps per channel transceivers • Redundant XAUI Serial Outputs • Low power consumption < 425mW per Channel • Compliant with 802.3ae spec features 10 Gigabit Ethernet • CML serial side i/f w/integrated termination • HSTL parallel I/O 10 Gigabit Ethernet • Flow through pin out • JTAG Support • Flip Chip Package Power TLK3118 3.2 Gbps/Ch <425mW/Ch Samples Now Next

Example: Backplane to Optics Implementation XAUI XGMII XGMII XAUI Back to SerDes Summary

Example: Optical Modules Cross Point or Backplane Optics Module Components CDR Frame/ Map Process E O Photo Detector Transimpedance Amplifier Post Amplifier Clock & Data Recovery DeMux Frame/ Map Process Clock Gen E O Laser Driver Laser Clock Generation Mux Back to SerDes Summary

Integrated Optical Modules Discrete devices can be replaced by a single Serdes like the SLK2501 Cross Point or Backplane SLK2501 Multi-Rate transceiver and CDR Frame/ Map Process E O Photo Detector Transimpedance Amplifier Post Amplifier Frame/ Map Process E O Laser Driver Laser Clock Generation Back to SerDes Summary

Multi Rate SONET TransceiversProviding the lowest power in the industry at the highest data rates • SLK2501 Multi-Rate SONET Transceiver • Complete Transceiver - mux, demux and CDR • Multi rate OC-3, 12, 24 (GBE), 48 support w/auto rate detect • Parallel interface: 4-bit LVDS / channel • Serial interface: PECL • Transmit only, Receive only, repeater and transceiver modes • On chip Termination for LVDS and PECL interfaces • Programmable Pre-Emphasis • Remote and Local Loop Back • 900mW power consumption (@ OC-48) (worse case) • Device Differences • SLK2721: SLK2701 with improved receiver tolerance • SLK2701: Multi-rate / OC-48 FEC Data rate up to 2.7 Gbps • SLK2511: SLK2501 with clock input 155MHz & 622MHz • SLK2501: Multi-rate with clock input 622MHz Power SLK2721 2.7Gbps/Ch < 900 mW SLK2701 2.7Gbps/Ch < 900 mW SLK2511 2.5 Gbps/Ch < 900 mW SLK2501 2.5 Gbps/Ch < 900 mW Back to SerDes Summary In Production

TXF100: 10 Gbps Serial Transceiver • Fully integrated signal conditioner on transmit and receive • Supports data rates of 9.95Gbps (SONET OC-192), 10.31Gbps (IEEE 802.3ae), 10.52Gbps (10GFC), 10.70Gbps (G.709), and 11.09Gbps (10GigE over G.709) • Integrated limiting amplifier with input sensitivity of 10 mVpp • Adaptive equalizer in transmit path accepts signals over 12 inch of FR4 • Horizontal eye-scan function on transmit and receive • CML interface with on chip termination • PRBS Generation and Verification • Line and XFI Loop Back • Low power CMOS technology – 500 mW power consumption • 32 pin QFN (5x5) • Samples 2Q04 Back to SerDes Summary

TOSA ROSA LAN PHY Solution Optics System XFI-XAUI Bridge XFP Module Traffic orQueue Manager Packet orNetwork Processor MAC orASIC XFI 10Gbps XAUI 3Gbps CDR TLK10021 - Device Description and Applications • XAUI to XFI PHY Device • 10 Gigabit Ethernet/10 Gigabit Fibre Channel Support • 800mW – Industry’s Lowest Power • Exceeds 10GBASE-R Jitter Generation and Tolerance • 144-pin Plastic BGA Package • 1.0mm Ball Pitch • Second source available • NDA Required for spec Back to SerDes Summary

LVDS SERDES Transmitters & Receivers 21:3 / 28:4 and 4:28 and 3:21 • LVDS Serdes Transmitters and Receivers • Transmitter and Receivers pairs for designing point to point links that support up to 1.82 Gbps of throughput • Transmitters accept LVTTL inputs on 21 or 28 parallel I/O and serialize data and convert into multiple LVDS channels • Receivers accept multiple LVDS channels from transmitters and are converted back to LVTTL and de-serialized to 21 or 28 parallel bits • Clock in frequency range: 20 - 65 MHz • compatible with cable or copper back-planes • Industrial Temp qualified • Drop in compatible second source available • EVM available SN65LVDS95/96 1.3 Gbps throughput SN65LVDS93/94 1.8 Gbps throughput In Production Next

LVDS SERDES Transmitters & Receivers21:3 / 28:4 and 4:28 and 3:21 SN65LVDS93: 28:4 (1.820Gbps) SN65LVDS95: 21:3 (1.365Gbps) SN65LVDS94: 4:28 (1.820Gbps) SN65LVDS96: 3:21 (1.365Gbps) DATA (LVDS) D A T A D A T A SERIAL TO PARALLEL PARALLEL TO SERIAL R Interface 28-bit or 21-bit D Interface 28-bit or 21-bit 140 – 455Mbps PARALLEL TO SERIAL SERIAL TO PARALLEL D R 140 – 455Mbps SERIAL TO PARALLEL PARALLEL TO SERIAL D R 140 – 455Mbps PARALLEL TO SERIAL SERIAL TO PARALLEL D R 140 – 455Mbps PHASE LOCKED LOOP PHASE LOCKED LOOP D R 20 – 65MHz CLK CLK CLOCK (LVDS) Back to SerDes Summary

LVDS SERDES Transmitters & Receivers10:1 and 1:10 • 10 bitLVDS Serdes Transmitters and Receivers • Transmitter and Receiver pair for designing links with following throughput: • 100-660 Mbps data (LV1023A/1224A) • * 120 -792 Mbps line speed (20% overhead for clock bits) • 100-400 Mbps data (LVDS1021/1212) • * 120-480 Mbps line speed (20% overhead for clock bits) • Clock in frequency range: • 30-66 MHz (1023/1224) • 10-66 MHz (1023A/1224A) (new) • 10-40 MHz (1021/1212) • Industrial Temp qualified • Drop in compatible second source for NSM DS92LV1023, DS92LV1224, DS92LV1021, DS92LV1212A at much lower power SN65LV1023A 100-660 Mbps transmitter SN65LV1224A 100-660 Mbps receiver SN65LV1021 100-400 Mbps transmitter SN65LV1212 100-400 Mbps receiver In Production Next

TX TX TX RX RX RX SN65LV1021/1023A SN65LVDS1021/1023 SN65LVDS1021/1023 SN65LVDS1212/1224 SN65LVDS1212/1224 SN65LV1212/1224A LVDS LVDS LVDS LVDS LVDS LVDS 10 10 10 A+ A+ A+ Y+ Y+ Y+ 10 10 10 Serial Serial Serial Parallel Parallel Parallel D D (LVTTL) (LVTTL) D D (LVTTL) (LVTTL) OUT OUT IN IN - - - A A A - - - Y Y Y - - - to to to - - - Output Latch Output Latch Output Latch - - - Input Latch Input Latch Input Latch to to to - - - TCLKR/F TCLKR/F TCLKR/F Parallel Parallel Parallel Serial Serial Serial TCLK TCLK REFCLK REFCLK Timing / Timing / Timing / Timing / Timing / Timing / REN REN PLL PLL PLL PLL PLL PLL Control Control Control DEN DEN Control Control Control LOCK LOCK LOCK SYNC1 SYNC1 RCLKR/F RCLKR/F RCLKR/F Clock Clock Clock SYNC2 SYNC2 Recovery Recovery Recovery RCLK RCLK LVDS SERDES Transmitters & Receivers 10:1 and 1:10 Architecture Note: (1021/1212) TCLK = 10MHz – 40MHz then LVDS serial line speed = 360-792 Mbps line speed* (1023A/1224A) TCLK = 10MHz – 66MHz then LVDS serial line speed = 120-480 Mbps line speed* * 20% overhead [10 data + 2 clock bits] Back to SerDes Summary

Serdes Solutions for Frontplane and Backplane TLK2201/1201/TLK2208/TLK2206 SLK2501/SLK2511/SLK2701/SLK2721 Low power 1 GbE Transceiver SONET OC-3 to OC-48 Txcvr with Mux, De-Mux, CDR and Clock 1-1.6 Gbps Line Module Clock Buffer Memory Photodiode TIA PA Back Plane Serdes NPU/ ASICs Front Plane Serdes MAC Framer/ Mapper Laser Diode LD Reference clock PLL Multiplier Clock Buffer TLK3114SA/SB – 10 Gigabit Ethernet back plane device “XAUI” 4 x 3.2Gbps TLK3118 – Redundant XAUI transceiver TLK2208 – 8 Channle Gigabit Ethernet Xcvr (8 x 1-1.3Gbps) TLK2206 – 6 Channel Gigabit Ether Xcvr (6 x 1-1.3 Gbps) with RTBI compliant interface TLK2201/TLK1201 – 1 to 1.6 Gbps Gigabit Ethernet complaint serdes TLK3101/TLK2501/TLK1501 – .6 to 3.2 Gbps General purpose back plane transceivers SN65LV1023/1224 – 300-660 mbps – 10:1 LVDS Serdes SN65LV1021/1212 – 100-400 mbps – 10:1 LVDS Serdes Back to SerDes Summary