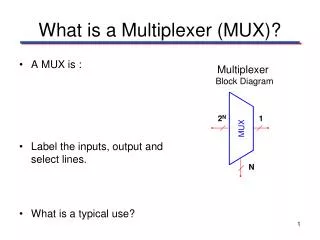

Multiplexer as a Universal Element

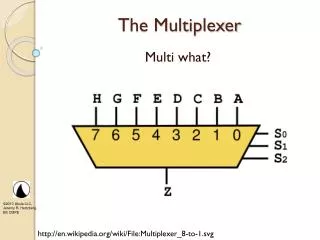

Multiplexer as a Universal Element. Discussion D2.6 Example 9. MUX as a Universal Element. Example. f = x*~y + x*z + ~y*z. Step 1. f = x*~y + x*z + ~y*z. If x = 0. f = v = ~y*z. If x = 1. f = w = ~y + z + ~y*z. Step 2. If x = 0. f = v = ~y*z. If y = 0. v = z. If y = 1. v = 0.

Multiplexer as a Universal Element

E N D

Presentation Transcript

Multiplexer as a Universal Element Discussion D2.6 Example 9

Example f = x*~y + x*z + ~y*z

Step 1 f = x*~y + x*z + ~y*z If x = 0 f = v = ~y*z If x = 1 f = w = ~y + z + ~y*z

Step 2 If x = 0 f = v = ~y*z If y = 0 v = z If y = 1 v = 0 If x = 1 f = w = ~y + z + ~y*z If y = 0 f = x*~y + x*z + ~y*z w = 1 If y = 1 w = z

-- Example 9: Using 2-to-1 MUXs -- as a universal function generator library IEEE; use IEEE.STD_LOGIC_1164.all; entity muxu is port( x : in STD_LOGIC; y : in STD_LOGIC; z : in STD_LOGIC; f : out STD_LOGIC ); end muxu; architecture muxu of muxu is component mux21b port( a : in std_logic; b : in std_logic; s : in std_logic; y : out std_logic); end component; signal v, w: STD_LOGIC;

begin M1 : mux21b port map( a => z, b => '0', s => y, y => v ); M2 : mux21b port map( a => '1', b => z, s => y, y => w ); M3 : mux21b port map( a => v, b => w, s => x, y => f ); end muxu;