Network On Chip Cache Coherency

Network On Chip Cache Coherency. Midterm presentation Students: Zemer Tzach Kalifon Ethan Instructor: Walter Isaschar Spring 2008. Project’s General Concepts. Network On Chip - Cache Coherency. General Background. Modern CPU’s are based on CMP - Multi-Core Processor.

Network On Chip Cache Coherency

E N D

Presentation Transcript

Network On Chip Cache Coherency Midterm presentation Students:ZemerTzach Kalifon Ethan Instructor: Walter Isaschar Spring 2008

Project’s General Concepts Network On Chip - Cache Coherency

General Background • Modern CPU’s are based on CMP - Multi-Core Processor. • Improved performance is achieved by “Distribution and Parallelism”. • Cores interact by using NoC – Network on Chip. Network On Chip - Cache Coherency

NoC’s General Diagram Network On Chip - Cache Coherency 4

NoC’s Characteristics Wormhole packet routing. Packet’s path is X-Y. Units can communicate simultaneously. Reduce power consumption. Scalability. Network On Chip - Cache Coherency 5

Cache Coherency Definition: CMP cores use only up to date data. Originally, Cache Coherency in CMP was achieved by using a central memory control unit. Network On Chip - Cache Coherency 6

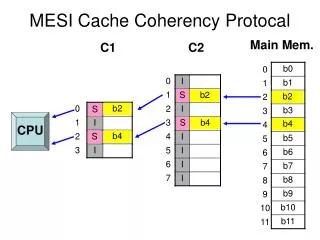

Cache Coherency Protocol Nowadays Network On Chip - Cache Coherency 7

Problem Description • Prior Cache Coherency protocols are irrelevant – NoC doesn’t have central unit. • Adding such unit will damage both NoC’s scalability and parallelism. Network On Chip - Cache Coherency

Solution Requirements • Won’t affect main NoC’s characteristics (e.g. scalability). • Avoid “Hot Spots” and “Bottle Necks”. • Minimize use of NoC’s resources. Network On Chip - Cache Coherency

Solution • Memory control distribution among a number of units according to memory spaces. • Placement of control units as part of the NoC. Network On Chip - Cache Coherency

Solution Diagram Network On Chip - Cache Coherency

Project’s Goals • Primary Goal: Design and implement Cache Coherency protocol for CMP. • Implement NoC (including NoC’s router). • Assemble CMP based on NoC. Network On Chip - Cache Coherency

Design Architecture Network On Chip - Cache Coherency

NoC Packet’s Structure • Packet is divided into flits. • There are four flit types: Start, Body, End and Idle. Network On Chip - Cache Coherency 14

Flit’s Structure • Flit contain two fields: Data and Type. Network On Chip - Cache Coherency 15

5 Ports Router • Direct packets according to X-Y routing. • 5 ports – North, East, West, South and Processing Unit. • Processing Units are using the network’s communication protocol. • 2 Virtual Channels per port. Network On Chip - Cache Coherency

5 Ports Router Structure Network On Chip - Cache Coherency 17

Input Port • Receives Flits from Router or from Processing unit. • Analyze and save the current packet direction. • Switch between Virtual Channels. Network On Chip - Cache Coherency

Input Port Structure Network On Chip - Cache Coherency 19

Output Port • Transmits Flits to Router or to Processing unit. • Each Virtual Channel save the currently serviced input port (CSIP). • Switch between Virtual Channels. Network On Chip - Cache Coherency

Output Port Structure Network On Chip - Cache Coherency 21

Cross Bar • Transfer Flits from Input Port to the matching Output Port. • Consists of 5 controllers – one for every Output Port. Network On Chip - Cache Coherency

Cross Bar Structure Network On Chip - Cache Coherency 23

Synthesis Parameters Network On Chip - Cache Coherency

Project Schedule (1st Semester) • Familiarize with design tools – 3 weeks. • Familiarize with VirtexII Pro FPGA (application & components) – 4 weeks. • Design & Implement NoC’s router – 5 weeks. • Assemble CMP using our router implementation – 2 weeks. Network On Chip - Cache Coherency

Project Schedule (2nd Semester) • Assemble CMP using our router implementation. • Design Cache Coherency protocol for CMP based on faculty research. • Implement the protocol as part of the assembled CMP. Network On Chip - Cache Coherency