Recap

This article explores the improvement in computational power through the use of multiprocessors versus uniprocessors, specifically in the context of summing large arrays of numbers. It discusses a sequential summation algorithm that runs in linear time and contrasts it with a parallel approach, utilizing N processors to divide the workload. Each processor computes a local sum for its assigned numbers and subsequently combines these partial sums to achieve the overall total. This highlights the efficiency gains achievable with multiprocessor architectures, leveraging shared and distributed memory systems.

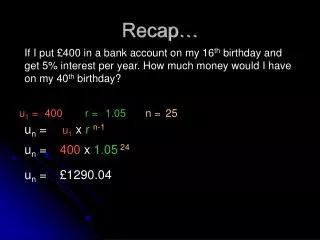

Recap

E N D

Presentation Transcript

Computational Power Improvement Multiprocessor Uniprocessor C.P.I 1 2 . . . . No. of Processors

Summing m Numbers Example: summing m numbers On a sequential computer we have, sum = a[0]; for (i=1;i<m;i++) { sum = sum + a[i]; } Would expect the running time be be roughly proportional to m.

Summing m Numbers in Parallel • What if we have N processors, with each calculating the m/N numbers assigned to it? • We must add these partial sums together to get the total sum.

Summing Multiprocessors Suppose we have N processors. • The algorithm is as follows: • Each processor finds the local sum of its m/N numbers • Each processor passes its local sum to another processor in a coordinated way • The global sum is finally in processor P11. P11 P12 P13 P21 P22 P23 i P31 P32 P33 j

MB MB P/C P/C Cache Cache NIC NIC Bus/Custom-Designed Network Shared Memory Multiprocessors Shared Memory

MPP (Massively Parallel Processing)Distributed Memory Multiprocessors MB : Memory Bus NIC : Network Interface Circuitry MB MB P/C P/C LM LM NIC NIC Custom-Designed Network

Cluster LD : Local Disk IOB : I/O Bus MB MB P/C P/C M M Bridge Bridge LD LD IOB IOB NIC NIC Commodity Network (Ethernet, ATM, Myrinet)

Grid P/C P/C P/C P/C IOC IOC Hub/LAN Hub/LAN NIC NIC LD LD SM SM SM SM Internet