Low-Level Programming

Low-Level Programming. ICOM 4036 Lecture 4. Prof. Bienvenido Velez. ALU. status. control. Practical Universal Computers ( John) Von Neumann Architecture (1945). Memory. CPU. Program. DataPaths. AC. This looks just like a TM Tape. PC. Data. ABR. Control Unit (FSM).

Low-Level Programming

E N D

Presentation Transcript

Low-Level Programming ICOM 4036 Lecture 4 Prof. Bienvenido Velez ICOM 4036 Programming Laguages Lecture 4

ALU status control Practical Universal Computers(John) Von Neumann Architecture (1945) Memory CPU Program DataPaths AC This looks just like a TM Tape PC Data ABR Control Unit (FSM) CPU is a universal TM An interpreter of some programming language (PL) ICOM 4036 Programming Laguages Lecture 4

Outline • The Von Neumann Architecture • From Voltages to Computers • Low-level Programming • Implementing HLL Abstractions • Control structures • Data Structures • Procedures and Functions ICOM 4036 Programming Laguages Lecture 4

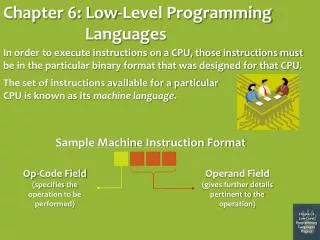

The (John) Von Neumann Architecture(late 40’s) Allow communication with outside world I/O devices Central Processing Unit (CPU) Interprets instructions Stores both programs and data Memory After 60 years … most processors still look like this! ICOM 4036 Programming Laguages Lecture 4

Interconnected registers, muxes, decoders, … The von Neumann ArchitectureCentral Processing (CPU) I/O devices Control Unit (FSM) Central Processing Unit (CPU) active control status Data Paths Memory passive ICOM 4036 Programming Laguages Lecture 4

The (John) Von Neumann ArchitectureThe Memory Unit word size I/O devices address space Central Processing Unit (CPU) Memory ICOM 4036 Programming Laguages Lecture 4

The (John) Von Neumann ArchitectureStored Program Concept Program Instructions Program Data • Programs and their data coexist in memory • Processor, under program control, keeps track of what needs to be interpreted as instructions and what as data. ICOM 4036 Programming Laguages Lecture 4

Easy IMemory Interface MEMORY CPU address data word memory op {R,W,NOP} ICOM 4036 Programming Laguages Lecture 4

I opcode X Easy IA Simple Accumulator Processor Instruction Set Architecture (ISA) Instruction Format (16 bits) 15 14 10 9 0 I = Indirect bit ICOM 4036 Programming Laguages Lecture 4

Easy IA Simple Accumulator Processor Instruction Set Architecture (ISA) Instruction Set Easy all right … but universal it is! ICOM 4036 Programming Laguages Lecture 4

Easy IData Paths (with control points) A bus is A D D R E S S B U S PC D A T A B U S sel sel 1 0 le DI A0 le A B op ALU AC le sel 0 1 ICOM 4036 Programming Laguages Lecture 4

Easy IA Simple Accumulator Processor Instruction Set Architecture (ISA) • Accumulator (AC) is implicit operand to many instructions. No need to use instruction bits to specify one of the operands. More bits left for address and opcodes. • Although simple, Easy I is universal. (given enough memory). Can you see this? • Immediate bit specifies level of indirection for the location of the operand. I = 1: operand in X field (immediate). I=1 operand in memory location X (indirect). Some Immediate Observations on the Easy I ISA ICOM 4036 Programming Laguages Lecture 4

Easy I - Control Unit Control Unit Combinational Logic EDBsel AC:15 AOle AOsel OpCode ACle DIle PCis I bit PCsel MEMop Current State ALUop Next State DataPaths + state 11 17 clock ICOM 4036 Programming Laguages Lecture 4

What makes a CPU cycle? CU Logic FSM logic state Data Paths Logic ALU, latches, memory Cycle time must accommodate signal propagation ICOM 4036 Programming Laguages Lecture 4

Easy I – Timing ExampleALU Operation CLK le DI DIle A B op ALU DIout AC le ALUout ACle ACout ICOM 4036 Programming Laguages Lecture 4

Easy IControl Unit(Level 0 Flowcharts) Fetch Read next instruction Decode Determine what it does and prepare to do it. Fetch operands. Execute Do it! We will ignore indirect bit (assuming I = 0) for now ICOM 4036 Programming Laguages Lecture 4

Easy IControl Unit(Level 1 Flowcharts) Reset Fetch Aopr Sopr Load Store BrN Jump What? Level 1: Each box may take several CPU cycles to execute ICOM 4036 Programming Laguages Lecture 4

RESET Easy IControl Unit(Level 2 Flowcharts) reset1 Byte Addressable Can you tell why? reset2 fetch Each box may take only one CPU cycle to execute ICOM 4036 Programming Laguages Lecture 4

aopr sopr load store brn jump FETCH Easy IControl Unit(Level 3 Flowcharts) Memory Bus Operation fetch Invariant At the beginning of the fetch cycle AO holds address of instruction to be fetched and PC points to following instruction 00 11x 00 00x 00 101 00 100 00 010 00 011 opcode Opcode must be an input to CU’s sequential circuit ICOM 4036 Programming Laguages Lecture 4

AOpr Easy IControl Unit(Level 2 Flowcharts) aopr Restore fetch invariant fetch ICOM 4036 Programming Laguages Lecture 4

SOpr Easy IControl Unit(Level 2 Flowcharts) sopr fetch ICOM 4036 Programming Laguages Lecture 4

Load Easy IControl Unit(Level 2 Flowcharts) load1 load2 load3 fetch ICOM 4036 Programming Laguages Lecture 4

Store Easy IControl Unit(Level 2 Flowcharts) store1 store2 fetch ICOM 4036 Programming Laguages Lecture 4

BrN Easy IControl Unit(Level 2 Flowcharts) brn1 Assume branch not taken. Allow AC:15 to propagate. AC:15 1 (AC<0) 0 (AC>0) brn2 fetch Can we accomplish all this in 1 cycle? How? Bit 15 of AC input to the CU’s sequential circuit ICOM 4036 Programming Laguages Lecture 4

Inside the Easy-I PC ABUS PC pcis 1 0 0 +2 Adder PC capable of loading and incrementing simultaneously 00 01 10 11 pcsel PC ICOM 4036 Programming Laguages Lecture 4

JUMP Easy IControl Unit(Level 2 Flowcharts) jump fetch ICOM 4036 Programming Laguages Lecture 4

Easy IData Paths (with control points) A bus is A D D R E S S B U S PC D A T A B U S sel sel 1 0 le DI A0 le A B op ALU AC le sel 0 1 ICOM 4036 Programming Laguages Lecture 4

Easy IControl Unit State Transition Table (Part I) ICOM 4036 Programming Laguages Lecture 4

Easy IControl Unit State Transition Table (Part II) CU with 14 states => 4 bits of state This is a (micro)program that interprets machine code ICOM 4036 Programming Laguages Lecture 4

Easy-I Control Unit – Some missing details 4-bit Encodings for States ALU Operation Table We know how to implement this ALU ! Control Bus Operation Table ICOM 4036 Programming Laguages Lecture 4

Easy IControl Unit State Transition Table (Part I) ICOM 4036 Programming Laguages Lecture 4

Easy IControl Unit State Transition Table (Part II) ICOM 4036 Programming Laguages Lecture 4

Building the Easy-I C-Unit2 Approaches • Harwired • Apply well known sequential circuit techniques • Micro-programmed • Treat state transition table as a program • Build a new abstraction layer A program The Microprogramming abstraction level ICOM 4036 Programming Laguages Lecture 4

Building the Easy-I C-UnitHardwired Approach Control Unit ROM control point signals next state 10 Memory Unit 2 control bus 11 state address bus data bus 4 Data Paths AC:15 5 DI<10:14> ICOM 4036 Programming Laguages Lecture 4

Computing Integer DivisionIterative C++ Version int a = 12; int b = 4; int result = 0; main () { if (a >= b) { while (a > 0) { a = a - b; result ++; } } } We ignore procedures and I/O for now ICOM 4036 Programming Laguages Lecture 4

DefinitionInstruction Set Architecture • What it is: • The programmers view of the processor • Visible registers, instruction set, execution model, memory model, I/O model • What it is not: • How the processors if build • The processor’s internal structure ICOM 4036 Programming Laguages Lecture 4

15 14 10 9 0 I opcode X Easy IA Simple Accumulator Processor Instruction Set Architecture (ISA) Instruction Format (16 bits) I = Indirect bit ICOM 4036 Programming Laguages Lecture 4

Easy IA Simple Accumulator Processor Instruction Set Architecture (ISA) Instruction Set ICOM 4036 Programming Laguages Lecture 4

Easy IMemory Model 8 bits 8 bits ICOM 4036 Programming Laguages Lecture 4

Computing Integer DivisionIterative C++ Version int a = 12; int b = 4; int result = 0; main () { if (a >= b) { while (a > 0) { a = a - b; result ++; } } } C++ HLL Easy-I Assembly Language ICOM 4036 Programming Laguages Lecture 4

Translate Data: Global Layout Computing Integer DivisionIterative C++ Version 0: andi 0 # AC = 0 addi 12 storei 1000 # a = 12 (a stored @ 1000) andi 0 # AC = 0 addi 4 storei 1004 # b = 4 (b stored @ 1004) andi 0 # AC = 0 storei 1008 # result = 0 (result @ 1008) int a = 12; int b = 4; int result = 0; main () { if (a >= b) { while (a > 0) { a = a - b; result ++; } } } • Issues • Memory allocation • Data Alignment • Data Sizing C++ HLL Easy-I Assembly Language ICOM 4036 Programming Laguages Lecture 4

Issues • Must translate HLL boolean expression into ISA-level branching condition Translate Code: Conditionals If-Then Computing Integer DivisionIterative C++ Version 0: andi 0 # AC = 0 addi 12 storei 1000 # a = 12 (a stored @ 1000) andi 0 # AC = 0 addi 4 storei 1004 # b = 4 (b stored @ 1004) andi 0 # AC = 0 storei 1008 # result = 0 (result @ 1008) main: loadi 1004 # compute a – b in AC comp # using 2’s complement add addi 1 add 1000 brni exit # exit if AC negative exit: int a = 12; int b = 4; int result = 0; main () { if (a >= b) { while (a > 0) { a = a - b; result ++; } } } C++ HLL Easy-I Assembly Language ICOM 4036 Programming Laguages Lecture 4

Translate Code: Iteration (loops) Computing Integer DivisionIterative C++ Version 0: andi 0 # AC = 0 addi 12 storei 1000 # a = 12 (a stored @ 1000) andi 0 # AC = 0 addi 4 storei 1004 # b = 4 (b stored @ 1004) andi 0 # AC = 0 storei 1008 # result = 0 (result @ 1008) main: loadi 1004 # compute a – b in AC comp # using 2’s complement add addi 1 add 1000 brni exit # exit if AC negative loop: loadi 1000 brni endloop jump loop endloop: exit: int a = 12; int b = 4; int result = 0; main () { if (a >= b) { while (a > 0) { a = a - b; result ++; } } } C++ HLL Easy-I Assembly Language ICOM 4036 Programming Laguages Lecture 4

Translate Code: Arithmetic Ops Computing Integer DivisionIterative C++ Version 0: andi 0 # AC = 0 addi 12 storei 1000 # a = 12 (a stored @ 1000) andi 0 # AC = 0 addi 4 storei 1004 # b = 4 (b stored @ 1004) andi 0 # AC = 0 storei 1008 # result = 0 (result @ 1008) main: loadi 1004 # compute a – b in AC comp # using 2’s complement add addi 1 add 1000 brni exit # exit if AC negative loop: loadi 1000 brni endloop loadi 1004 # compute a – b in AC comp # using 2’s complement add addi 1 add 1000 # Uses indirect bit I = 1 jumpi loop endloop: exit: int a = 12; int b = 4; int result = 0; main () { if (a >= b) { while (a > 0) { a = a - b; result ++; } } } C++ HLL Easy-I Assembly Language ICOM 4036 Programming Laguages Lecture 4

Translate Code: Assignments Computing Integer DivisionIterative C++ Version 0: andi 0 # AC = 0 addi 12 storei 1000 # a = 12 (a stored @ 1000) andi 0 # AC = 0 addi 4 storei 1004 # b = 4 (b stored @ 1004) andi 0 # AC = 0 storei 1008 # result = 0 (result @ 1008) main: loadi 1004 # compute a – b in AC comp # using 2’s complement add addi 1 add 1000 brni exit # exit if AC negative loop: loadi 1000 brni endloop loadi 1004 # compute a – b in AC comp # using 2’s complement add addi 1 add 1000 # Uses indirect bit I = 1 storei 1000 jump loop endloop: exit: int a = 12; int b = 4; int result = 0; main () { if (a >= b) { while (a > 0) { a = a - b; result ++; } } } C++ HLL Easy-I Assembly Language ICOM 4036 Programming Laguages Lecture 4

Translate Code: Increments Computing Integer DivisionIterative C++ Version 0: andi 0 # AC = 0 addi 12 storei 1000 # a = 12 (a stored @ 1000) andi 0 # AC = 0 addi 4 storei 1004 # b = 4 (b stored @ 1004) andi 0 # AC = 0 storei 1008 # result = 0 (result @ 1008) main: loadi 1004 # compute a – b in AC comp # using 2’s complement add addi 1 add 1000 brni exit # exit if AC negative loop: loadi 1000 brni endloop loadi 1004 # compute a – b in AC comp # using 2’s complement add addi 1 add 1000 # Uses indirect bit I = 1 storei 1000 loadi 1008 # result = result + 1 addi 1 storei 1008 jumpi loop endloop: exit: int a = 12; int b = 4; int result = 0; main () { if (a >= b) { while (a > 0) { a = a - b; result ++; } } } C++ HLL Easy-I Assembly Language ICOM 4036 Programming Laguages Lecture 4

Computing Integer DivisionEasy I Machine Code Data Program Challenge Make this program as small and fast as possible ICOM 4036 Programming Laguages Lecture 4

The MIPS ArchitectureISA at a Glance • Reduced Instruction Set Computer (RISC) • 32 general purpose 32-bit registers • Load-store architecture: Operands in registers • Byte Addressable • 32-bit address space ICOM 4036 Programming Laguages Lecture 4

The MIPS Architecture32 Register Set (32-bit registers) ICOM 4036 Programming Laguages Lecture 4

The MIPS ArchitectureMain Instruction Formats • Simple and uniform 32-bit 3-operand instruction formats • R Format: Arithmetic/Logic operations on registers • I Format: Branches, loads and stores • J Format: Jump Instruction funct 6 bits opcode 6 bits rs 5 bits rt 5 bits rd 5 bits shamt 5 bits opcode 6 bits rs 5 bits rt 5 bits Address/Immediate 16 bits opcode 6 bits rs 5 bits rt 5 bits Address/Immediate 16 bits ICOM 4036 Programming Laguages Lecture 4

![[Low-level] Programming of NXT Robots](https://cdn0.slideserve.com/1257924/slide1-dt.jpg)