Power Aware Synthesis

Power Aware Synthesis. Virendra Singh Indian Institute of Science Bangalore virendra@computer.org. IEP on Digital System Synthesis @ IIT Kanpur. High Level Synthesis. Objective Area Performance Power Reliability. Power. Dynamic Power Static Power Transitions

Power Aware Synthesis

E N D

Presentation Transcript

Power Aware Synthesis Virendra Singh Indian Institute of Science Bangalore virendra@computer.org IEP on Digital System Synthesis @ IIT Kanpur

High Level Synthesis • Objective • Area • Performance • Power • Reliability PCS@iitk

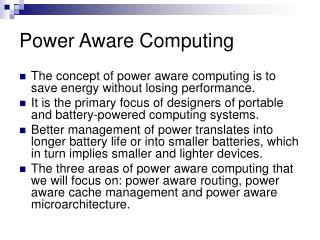

Power • Dynamic Power • Static Power • Transitions • Large fraction of transitions incurred during the circuit operation are unnecessary • Suppressing or eliminating unnecessary transitions PCS@iitk

Power Reduction Techniques • Techniques • Clock gating • Partitioning of circuits • Scheduling – to maximize idle time • Maximize the sleep time of storage elements PCS@iitk

Power Reduction Techniques During the control steps in which functional unit is utilized to perform some operation is said to be active During other control steps, the functional unit is said to be idle The manner in which register sharing is performed can significantly affect the unnecessary power dissipation (spurious switching) in functional units during their idle cycle PCS@iitk

Effect of Register Sharing Architectural Model Register Allocation and variable assignment Effect on switching activity Spurious switching activities can sometimes be eliminated without increasing the number of registers in synthesized circuit PCS@iitk

Scheduled DFG v1 v5 v15 v2 v2 v4 +1 ADD1 *3 MUL2 *1 MUL1 S1 v8 v3 v7 v6 +2 ADD1 -1 SUB1 v10 S2 v11 v9 -2 SUB1 ADD1 v14 +3 S3 v13 *2 MUL1 S4 v15 6 7 S5 PCS@iitk

Variable Assignment PCS@iitk

Switching Activity PCS@iitk

Switching Activity PCS@iitk

Scheduled DFG v1 v2 v3 v4 +1 *1 MUL1 ADD1 S1 v6 v5 +2 ADD1 S2 v8 v7 ADD1 +3 v9 S3 v10 *2 MUL1 S4 v11 6 7 S5 PCS@iitk

Variable Assignment PCS@iitk

Power Management using Latches b a 1 h c 2 j i 1 k PCS@iitk