Understanding Memory Hierarchy: Principles, Trends, and Design in Modern Processors

This chapter delves into the memory hierarchy, exploring the critical role it plays in processor performance. It discusses the latency gap faced during cache misses and the importance of managing memory to optimize speed and efficiency. Key concepts such as cache hits and misses, associativity, and interleaving are analyzed along with technology trends shaping memory systems. The text outlines how different levels of memory interact and the trade-offs involved in their design, aiming to enhance cache performance and manage virtual memory effectively.

Understanding Memory Hierarchy: Principles, Trends, and Design in Modern Processors

E N D

Presentation Transcript

Processor Memory Latency Gap Time of a full cache miss in instructions executed • 1st Alpha: 340 ns/5.0 ns = 68 clks x 2 (136 instr.) • 2nd Alpha: 266 ns/3.3 ns = 80 clks x 4 (320 instr.) • 3rd Alpha: 180 ns/1.7 ns =108 clks x 6 (648 instr.)

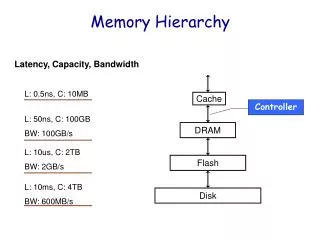

Solution: Memory Hierarchy Speed: Fastest Slowest Size: Smallest Biggest Cost: Highest Lowest

How Does It Work? Speed (ns): 1’s 10’s 100’s 10,000,000’s 10,000,000,000’s (10’s ms) (10’s sec) Size(bytes): 100’s K’s M’s G’s T’s

Block Size Block Size Tradeoff