Enhanced Verification by Temporal Decomposition

This paper presents a methodology for enhancing gate-level property checking by simplifying designs through the elimination of transient signals. Transient signals can lead to erroneous states in digital systems, and understanding their origin is crucial for effective verification. The authors, Mike Case, Hari Mony, Jason Baumgartner, and Bob Kanzelman, discuss methods to detect and eliminate these signals, the role of initialization inputs, and provide experimental results showcasing the prevalence of transients in real-world designs. The findings demonstrate significant improvements in verification processes using temporal decomposition techniques.

Enhanced Verification by Temporal Decomposition

E N D

Presentation Transcript

Enhanced Verification byTemporal Decomposition Mike Case, Hari Mony, Jason Baumgartner, Bob Kanzelman FMCAD 2009, Nov. 16, 2009

[XKCD] Introduction • Domain: gate-level property checking (and SEC) • Problem: simplify the design; remove irrelevant detail Mike Case

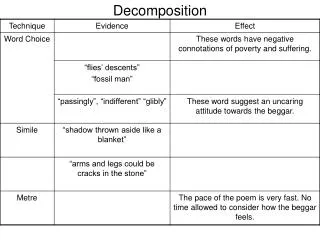

Outline • Transient Signals • What are they and where do they come from? • How to eliminate them • Initialization Inputs • What are they and where do they come from? • How to eliminate them • Experimental Results Mike Case

Outline • Transient Signals • What are they and where do they come from? • How to eliminate them • Initialization Inputs • What are they and where do they come from? • How to eliminate them • Experimental Results Mike Case

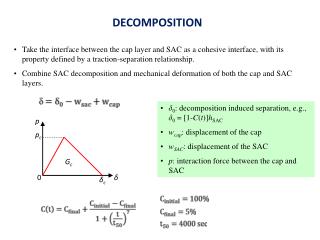

0 0 0 0 0 0 0 0 1 1 1 1 1 Transient Signals • Definition: a transient signal takes arbitrary values for a finite number of clock cycles and then assumes a fixed constant value Time 0 1 2 3 4 5 Register A Register B Register C Transient Mike Case

0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 Transient Transient Why Do They Occur? – Initialization Sequences Time 0 1 2 3 4 5 Transient Pulsed Reset Register A Register B Register C Mike Case

Driver Checker Why Do They Occur? – Verification Testbenches • Testbench → all FPU signals are transient FPU Pipeline Testbench Time 0: MUL NOP NOP NOP Time 1: NOP MUL NOP NOP Design Under Test Time 2: NOP NOP MUL NOP Time 3: NOP NOP NOP MUL Time >3: NOP NOP NOP NOP Mike Case

How Common Are Transient Signals? • On 105 “hard” IBM designs: 49% had transients • On 27 “hard” HWMCC designs: 25% had transients Mike Case

Outline • Transient Signals • What are they and where do they come from? • How to eliminate them • Initialization Inputs • What are they and where do they come from? • How to eliminate them • Experimental Results Mike Case

Time 1: State=0X1X, Inputs=XX Time 2: State=X00X, Inputs=XX Transient Time 3: State=X0XX, Inputs=XX Time 4: State=X00X, Inputs=XX Detecting Transients With Ternary Simulation Ternary Sim. Execution Abstract State Space Time 0: State=0000, Inputs=XX Fast, but incomplete Mike Case

0 0 0 0 1 Maximum Transient Duration Check with unbounded model checking Check with BMC Time 0 1 2 3 4 5 Temporal Decomposition For Verification • Definition: the transient duration is the number of time steps before a transient settles to its constant value Time Transient with duration 2 0 1 2 3 4 5 Register C Mike Case

Prop. Simplify Transient Signals Transition Relation inp1 Initial Values Transition Relation N Max. Transient Duration Transition Relation inp2 init1 init2 inp3 Time Shifting for Unbounded Verification • Modeling: a register’s initial values is an arbitrary combinational function Prop. Next States Transition Relation Registers Initial Values init1 init2 inp. • New design starts in any state reachable in N steps. Mike Case

Simplification Results • Resources limit the transients that can be simplified • TR decreases • Initialization logic increases Mike Case

Outline • Transient Signals • What are they and where do they come from? • How to eliminate them • Initialization Inputs • What are they and where do they come from? • How to eliminate them • Experimental Results Mike Case

input input input input We have lots of initialization inputs • Definition: an initialization input is a primary input that is only needed to compute the initial state Prop. Next States Transition Relation Registers Initial Values input Initialization Inputs Mike Case

Prop. Transition Relation inp1 Transition Relation • We created initialization inputs! inp2 Transition Relation init1 init2 inp3 Transient Simplification Creates Initialization Inputs Mike Case

Outline • Transient Signals • What are they and where do they come from? • How to eliminate them • Initialization Inputs • What are they and where do they come from? • How to eliminate them • Experimental Results Mike Case

Unchanged Prop. Next States (might change) Transition Relation Registers Initial Values (might change) input input input input input 0 Initialization and Observability • Definition: a signal X is observable at signal Y if a toggle at X can cause a toggle at Y • Approximate with structural analysis • Simplify initialization inputs that arenever observable at any property Mike Case

input primary inputs Prop. TR input input Currstates Nextstates input input Frame 0 0 0 0 0 input input Simplification of Initialization Inputs: High Level • No initialization inputs observable at Prop0 • Two initialization inputs un-observable at Next0 → Un-observable at Propj j > 0 Prop. Next States BMC Transition Relation Registers Initial Values input input input Mike Case

input primary inputs Prop. TR Currstates Nextstates Frame 1 0 0 Simplification of Initialization Inputs: High Level Prop. Next States input BMC Transition Relation primary inputs Prop. Registers TR input Initial Values input input Currstates Nextstates 0 0 Frame 0 • No initialization inputs observable at Prop0 • Initialization inputs maybe observable at Next1 → Maybe observable at Propj j > 1 input input Mike Case

Simplification Results Fast, but incomplete Mike Case

Outline • Transient Signals • What are they and where do they come from? • How to eliminate them • Initialization Inputs • What are they and where do they come from? • How to eliminate them • Experimental Results Mike Case

Note: this is a systematic improvement on a large benchmark suite, not a collection of anecdotal examples Runtime of our Methods + BMC Results • Two methods presented: • Transient Simplification – Runtime capped at 10 seconds • Initialization Input Simplification – Runtime capped at 10 seconds • Tested on 105 “hard” industrial designs and 27 “hard” academic designs • Largest was 632K ands and 97K registers Mike Case

Synthesis Results Mike Case

Verification Results • Induction results: • Transient logic often breaks induction • Our methods can render problems inductive • Design 1: 22k Ands and 800 registers, solvable in 42 sec • Design 2: 20k Ands and 3k registers, solvable in 56 sec Mike Case

Conclusion • Transient and Initialization Input Simplification • Fast running • Benefits synthesis and verification Thank You Mike Case