Chapter 5 Interrupt

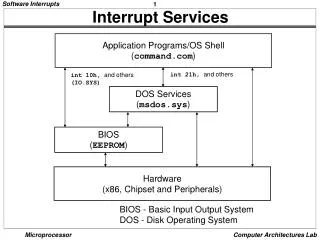

Chapter 5 Interrupt. INTERRUPTS. is an event that requires the CPU to stop normal execution and perform some service related to the event. . Interrupt Structure. The PIC18F microcontrollers support multiple interrupts: internal interrupts external interrupts. . Interrupt Structure.

Chapter 5 Interrupt

E N D

Presentation Transcript

Chapter 5 Interrupt

INTERRUPTS is an event that requires the CPU to stop normal execution and perform some service related to the event.

Interrupt Structure • The PIC18F microcontrollers support multiple interrupts: • internalinterrupts • externalinterrupts.

Interrupt Structure • Interrupt priority • allows interrupt sources to be assigned • a high-priority level will branch to 0x0008h • a low-priority level will branch to 0x0018h

Interrupt Structure • High-priorityinterrupt events will interrupt any low-priority interrupts. • Low-priority interrupts are not processed while high-priority interrupts are in progress.

Interrupt Structure • Each interrupt has an individual interrupt flag andmask bit. • It has an associated • request bit (IF), • enable bit (IE) and • priority bit (IP).

Interrupt Structure • All the interrupts can be • enabledby setting or • disabledby clearing the GIE bit. 7

Interrupt Structure • It supports two modes: • Legacy mode: • supports only 1 interrupt vector and • branches to 0x00008h for others. • can be selected by clearing the IPEN bit in RCON register.

Interrupt Structure There are ten registers which are used to control interrupt operation. These registers are: • RCON • INTCON • INTCON2 • INTCON3 • PIR1 • PIR2 • PIE1 • PIE2 • IPR1 • IPR2

Interrupt Structure • Interrupt sources have 3 bits to control their operation. They are: • Flag bit to indicate that an interrupt event occurred. • Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set. • Priority bitto selecthigh priority or low priority.

The Interrupt Priority • is enabled by setting the IPEN bit (RCON<7>). • When interrupt priority is enabled, there are two bits which enable interrupts globally.

The Interrupt Priority • Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set. (high priority). • Setting the GIEL bit(INTCON<6>) enables all interrupts that have the priority bit cleared. (low priority).

The Interrupt Priority • When the IPEN bit is cleared (default state), the interrupt priority feature is disabled. • INTCON<6> is the PEIE bit, which enables/disables all peripheral interrupt sources. • INTCON<7> is theGIE bit, which enables/disables all interrupt sources.

The Interrupt Priority • All interrupts branch to address 0008h in Compatibility mode. • The “return from interrupt” instruction, RETFIE, exits the interrupt routine and sets the GIE bit which re-enables interrupts..

RCON Register • Bit (IPEN) to enable interrupt priority • The other bits are used to indicate the cause of reset.

INTCON Registers • These 3 registers contain • enable, • priority and • flag bits for • external INT pins, • portB pin change and • TIMER0 (TMR0) overflow interrupts.

REGISTER 5-2: INTCON: INTERRUPT CONTROL REGISTER INTCON Registers INTCON: INTERRUPT CONTROL REGISTER INTCON2: INTERRUPT CONTROL REGISTER2 INTCON3: INTERRUPT CONTROL REGISTER

INTx Pin Interrupts • edge-triggered. • If the corresponding INTEDGx bit in the INTCON2 register is • set (= 1),the interrupt is triggered by a rising edge; • cleared (= 0),the trigger is on the falling edge.

TMR0 Interrupt • In 8-bit mode • an overflow in the TMR0 register (FFh→00h) will set flag bit, TMR0IF. • In 16-bit mode • an overflow in the TMR0H:TMR0L register pair (FFFFh →0000h) will set flag bit,TMR0IF. • The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE (INTCON<5>).

PORTB Interrupt-on-Change • An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). • The interrupt can be enabled/disabledby setting/clearing enable bit, RBIE (INTCON<3>). • Interrupt priority for PORTB interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP (INTCON2<0>).

RESET The main function is to establish appropriate values for key registers so that the MCU can start or restart properly.

RESET • The PIC18 MCU differentiates between various kinds of reset: • Power-On reset (POR). • MCLR pin reset during normal operation. • MCLR pin reset during SLEEP. • Watchdog timer (WDT) reset. • Programmable brown-out reset (BOR). • RESET instruction. • Stack Full reset. • Stack Underflow reset.