Market Evaluation and Use Planning for Highly Accurate ADC in ASIC/ASSP Industry

E N D

Presentation Transcript

Use Plan • WP 5: Dissemination and implementation • Task 5.1: Market evaluation and use planning Use planning in AMI Semiconductor Belgium

AMIS Use Plan: Outline • Highly accurate ADC in ASIC/ASSP • ASIC / ASSP market data analysis • Trends analogue SoC • Technical challenges analogue SoC testing • Valorisation potential

Highly Accurate A/D converter in ASIC • Resolution of 15 bit or higher, moderate sample rates • Usage in ASIC made realistic by: • New A/D architectures, e.g. sigma-delta • Design techniques for low power • On-chip digital signal processing capable to handle the digital signal

Highly accurate A/D converter in AMIS • Today standard accuracy is 12 bit • New sensor interfaces require 16 – 17 bit resolution, e.g. • Gyroscope • Acceleration sensor • Intelligent battery sensor • Making the systems more intelligient and autonomous requires more accurate information

SoC test: technical challenges • SoC era extremely challenging for test • Reduce test time while quality level must go up • Reduce test development time • All internal circuit blocks have to be “observable” to enable design debug • Scan, BIST, parallel testing are helpful for logic SoC but not for the analog blocks

Test cost challenges • Test cost equal the processing cost ?? Source: ITRS roadmap

Model for Valorisation • Use of highly accurate A/D converter • The served market are the automotive and industrial segments in the analog / mixed-signal ASIC / ASSP market • Reference value 2003: 4.1 B.EUR (4.6 B.USD) • Use of test techniques • The served market is the total analog / mixed-signal ASIC / ASSP market • Reference value 2003: 14.3 B.EUR (15.7B.USD) • Same market segments for AMIS Belgium business

Valorisation A/D Converter Case AMIS Europe

Valorisation A/D Converter Case Global business

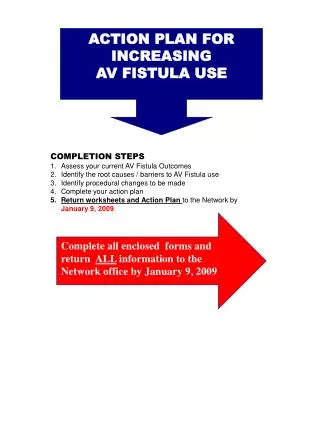

Use Plan test techniques AMIS GAIN 1: test is 30% manufacturing cost, reduce by 10 % GAIN 2: time to test ADC is 3 sec, reduce by 1.5 sec

Conclusion valorisation for AMIS-B • Growing need for highly accurate ADC • AMIS Business affected by 2009 forecasted 16.6 MUSD • Use know-how, design methodology & tools, subcontracting • High impact of accurate ADC testing on total manufacturing cost • Predicted cost saving for 2009 between 6.4 and 10.2 MUSD based on modest gains in test time • Cost saving could already start in 2005