Enhancing Signal Integrity Detection on SoC Interconnects Using Wrapper Designs

This paper presents innovative wrapper designs aimed at improving signal integrity (SI) fault detection on core external interconnects of System-on-Chips (SoCs). We address critical issues such as overshoot detection and crosstalk, which have become more pronounced with technology scaling. Our proposed overshoot detector features a self-biased amplifier and maintains hysteresis properties for reliable fault detection across various conditions. Experimental results demonstrate the effectiveness of our designs in mitigating signal integrity problems while balancing test time and area overhead.

Enhancing Signal Integrity Detection on SoC Interconnects Using Wrapper Designs

E N D

Presentation Transcript

Test Wrapper Designs for the Detection of Signal Integrity Faults on Core External Interconnects of SOCs Qiang Xu and Yubin Zhang Krishnendu ChakrabartyTheChinese University of Hong Kong Duke University

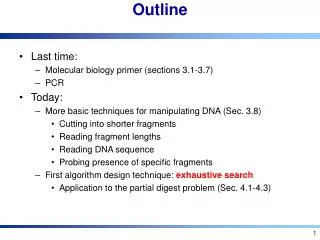

Outline • Introduction • Prior work and motivation • Overshoot detector • Wrapper design for interconnect SI test • Experimental results • Conclusion

Impact of Technology Scaling Interconnect Crosstalk Serious crosstalk Shrinking feature size

Signal Integrity Problem Signal integrity is a major concern!

Typical WOC for Interconnect SI Test • Simultaneous aggressor transitions in test mode • Different from functional mode

Impact of Aggressor Alignment on Crosstalk • Transition timing of aggressors/victim significantly affects signal integrity • Need for skewed transitions to avoid under-testing

Prior Overshoot Detector • Cross-coupled differential amplifier • Test_Mode signal as control of source current • Hysteresis property • Input-dependent detection • Cannot detect overshoot in all cases! Source: M. Nourani and A. Attarha, TCAD’02

Motivation • Prior SI test techniques • simultaneous transitions in test mode may result in under-testing. • cannot detect overshoot in all cases. • We need • wrapper input cell that can detect overshoot and delay faults in all cases. • wrapper output cellthat can apply skewed transitions.

Proposed Overshoot Detector • Maintain hysteresis property • Self-biased amplifier, higher resolution • Reset mechanism • Can detect overshoot in all cases

Wrapper Input Cell • Equipped with overshoot detector • One extra FF as delay detector (FF1).

Wrapper Input Cell • Equipped with overshoot detector • One extra FF as delay detector (FF1). • Save test data

Wrapper Input Cell • Equipped with overshoot detector • One extra FF as delay detector (FF1). • Save test data • Shift out result

Test Strategy I Functional path

Test Strategy II Test path

Experimental Setup • 90 nm technology with 1V power supply • 5 mm long victim with 5 aggressors, each coupling for a 1 mm length • On the eighth metal layer with typical parameter

Experimental Results with Proposed WOC with 2 delay paths with 4 delay paths 0.614 ns 0.595 ns

Experimental Results with Proposed WOC – Cont. with 6 delay paths with 8 delay paths 0.622 ns 0.627 ns

Discussion • Benefits • Enhanced signal-integrity fault detection capability • Costs • DfT area overhead • test time • Possible over-testing

Conclusion • Signal integrity is a major concern for today’s SoC interconnects • We have proposed novel test wrappers that • Detect all kinds of overshoots • Apply skewed-transitions for aggressors/victim groups • Have moderate overhead