Improving PLL Lock and Signal Pattern Testing with TLK10232

This document discusses the process of achieving PLL lock with the TLK10232 device, including configuration recommendations to enhance signal patterns. It outlines the ideal direct connection methods for testing and emphasizes the importance of minimizing error counts during bit error rate (BER) tests. Additionally, the document details the use of DCA (Digital Communication Analyzer) for eye pattern testing with SFP+ modules, thereby providing insights into testing methods that can improve signal quality and system performance.

Improving PLL Lock and Signal Pattern Testing with TLK10232

E N D

Presentation Transcript

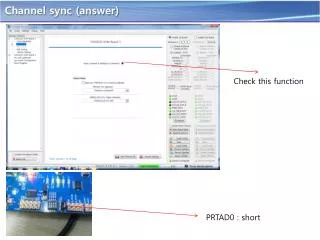

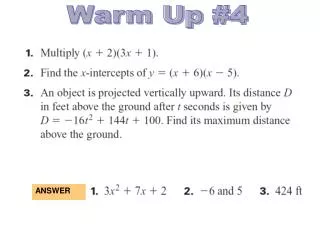

Channel sync (answer) Check this function PRTAD0 : short

Read register 0x0f (answer) Receiving PLL Lock

TLK10232 ( question ) Loading your config => can improve pattern signal ??? I will check again but I’d like to know your opinion that can improve ?

TLK10232 ( BER_Test) Current count I think, Should be no error count When I use direct connection method. Direct Connection HSTXBp and HSRXBp

TLK10232 ( answer) SFP+ eye pattern Test method DCA trigger : using TLK10232 EVM clock Put SFP+'s Tx part(optics) in DCA optical module part.