The L0 Calorimeter Trigger

The L0 Calorimeter Trigger. U. Marconi On behalf of the Bologna Group CSN1, Catania 16/9/02. Calorimeter Trigger. LHCb Trigger Performances. L1 Trigger using L0 information. L0 Calorimeter Trigger – L1 Trigger. L1-Trigger With p T info. Calorimeter Trigger Basic Principles.

The L0 Calorimeter Trigger

E N D

Presentation Transcript

The L0 Calorimeter Trigger U. Marconi On behalf of the Bologna Group CSN1, Catania 16/9/02

Calorimeter Trigger INFN Sezione di Bologna

LHCb Trigger Performances L1 Trigger using L0 information INFN Sezione di Bologna

L0 Calorimeter Trigger – L1 Trigger L1-Trigger With pT info INFN Sezione di Bologna

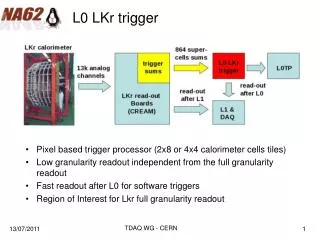

Calorimeter Trigger Basic Principles • Identify hot spots • Detect a high energy in a smallsurface • Use a square of 2 x 2 cells area • 8 x 8 cm2 in the central region of ECAL (may loose a few % of the energy) • more than 50 x 50 cm2 in the outer region of HCAL • Select the particles with the highest ET • Due to its high mass, a B particle decays into high PT particles • 'High PT ' is a few GeV • For the Level 0 decision, we need the particle with the highest PT (the second highest also in HCAL) INFN Sezione di Bologna

Select locally the highest candidate (reducing complexity and cabling) • Process further only the local candidates • ~200 for ECAL and ~50 for HCAL starting from 6000 and 1500 cells. • Validate the candidates • Electron, photon, 0: • Electromagnetic nature using the PreShower • Charge using the SPD • Hadron • Add the energy lost in ECAL in front of the HCAL candidate, looking only at ECAL candidates (manageable number of connections) INFN Sezione di Bologna

Select the highest validated candidates • One wants the highest ET candidates • Ghosts removal • Second highest for hadrons • No need for a second highest for electron or photon. • The processing is entirely synchronous • No dependence on occupancy and history • Easier to understand and to debug • Pipeline processing at all stages. INFN Sezione di Bologna

Hardware Implementation • About 6000 ECAL cells (as well as for the PreShower and the SPD) • Variable cell size, identical structure for SPD/PreShower /ECAL • HCAL different, see later • Front-end electronics located on top of the detector • Use SEU immune components (order of 100 rads/year) • 32 channels per FE card for ECAL/HCAL, 64 for Prs/SPD • Minimal cabling complexity • Use a dedicated backplane for as many connections as possible • 8 bits ET converted from the 12 bits ADC. • 8 bits are adeguate with a full scale limit around 5 GeV. INFN Sezione di Bologna

First selection • Build the 2x2 sums • Work inside a 32 channels (8x4) front-end card • To obtain the 32 2x2 sums, one needs to get the 8 + 1 + 4 neighbours • Via the backplane (9) or dedicated point-to-point cables(4) INFN Sezione di Bologna

Block diagram of the Front_End Board (LAL-ORSAY) INFN Sezione di Bologna

ECAL Validation • For each ECAL candidate, one needs toaccess the SPD and the PreShowerinformation (2 times 4 bits for the SPD&Preshower cells corresponding to the ECAL candidate) • The address is sent from the ECAL to the PreShower FE bords • One PreShower board handles 64 channels (exactly 2 ECAL boards) • The 24 bits are extracted synchronously at each BX and sent to the Validation Card INFN Sezione di Bologna

ECAL Validation produces 4 candidate types • Electrons and photons are validated FE-candidates • ‘local 0’ is detected as a high total energy on a card • ‘global 0’ is detected by summing the energies of two FE-candidates of two adjacent cards. • No SPD/PreShower validation foreseen for the 0, but this will be integrated in the card, in case… • This is just a few more output bits of the previous LUT, plus the validation of a register. • Only the highest Et ECAL candidate is interesting • We select the highest of the 8 on the Validation card • Output 4 ECAL candidates • Each has 8 bits Et and 8 bits address, plus BX-ID. INFN Sezione di Bologna

HCAL Validation • Ideal case: Add the ECAL cells in front of the HCAL candidate, but this implies a lot of connections, at 40 MHz. • This addition is important only if the ECAL energy deposit is large, then likely, it also has a large chance to be detected as a local maximum in the ECAL FE-board. • Send the 50 HCAL candidates to the ECAL ones • Less connections, some duplication, but we can use the ECAL Validation Card. • One ECAL FE-board matches only one HCAL card. • One validation card receives at most four HCAL cards • One HCAL card goes at most (30 of 50) to two Validation cards INFN Sezione di Bologna

Validation board LAL ORSAY INFN Sezione di Bologna

The Optical Links • The Optical Links are used to transmit the calorimeter-clusters from the Validation Cards to the Selection Crate • The total amount of the optical channels • 16 (SPD) + 428 (ECAL) + 80 (HCAL) = 208 Ch • Cluster bit patterns • HCAL: 8 bits (BX) + 8 bits (ET) + 5 bits (Address) • ECAL: 8 bits (BX) + 8 bits (ET) + 8 bits (Address) • SPD: 8 bits (BX) + 10 bits (Mult.) INFN Sezione di Bologna

Optical Link. Tx/Rx Prototypes Optical Tx 32-bits Data Input G-Link Serial Protocol Power Consumption 2.5W Rx PLD Clock Optical Tx/Rx INFN Sezione di Bologna

Optical Tx/Rx. Bit Error Rate Measurements Clock Jitter Characteristics External Clock Bit-Pattern and Control-bits Generator To the Optical Rx Pick-to-pick: 220 ps : 34.2 ps INFN Sezione di Bologna

Optical Tx/Rx. Test Setup VME Pattern Unit Control-Board Optical Channel Tx/Rx Overall Latency 500 ns Tx: 1 clock cycle Rx: 3 clock cycles Recovery Time ~1ms INFN Sezione di Bologna

40.00 MHz 33120 Agilent Noise Generator PMT5193 PG9210 LC584 Vpp(mV) Philips PM5193 Function Generator And Modulator Le Croy PG9210 Pulse Generator BER vs Jitter Glink Optical Channel Jitter Modulation Ext. Trigger Sine Wave 40MHz Clock with jitter Ext. Modulation Le Croy LC584 Oscilloscope INFN Sezione di Bologna

TRANSMIT 32 bits @ 40 MHz GOL (Gigabit Optical Link) Optical Transmitter (FTRJ-8519-1-2.5) Data in Clock Optical Fibre 1.2 Gb/s 40 MHz RECEIVE Power Consumption 360mW 16 bits @ 80 MHz 32 bits @ 40 MHz Data out Demultiplexer TLK2501 Optical Receiver (FTRJ-8519-1-2.5) Clock 40 MHz Max peak-to-peak Jitter 40ps INFN Sezione di Bologna

GOL Tx Scheme INFN Sezione di Bologna

40.00 MHz 33120 Agilent Noise Generator PMT5193 PG9210 LC584 Vpp(mV) Jitter Filter by PLL The best Jitter we can achieve now ~16ps rms Le Croy LC584 Oscilloscope ITD5993A ITD 5993 PLL Filter Philips PM5193 Function Generator And Modulator Le Croy PG9210 Pulse Generator INFN Sezione di Bologna

The Selection Crate • The 4 ECAL types are processed the same way • The complete cluster-address assignement is performed • The highest of the 28 inputs for each cluster type is selected and sent to the L0DU • The HCAL processing • Cluster copies are removed, the highest is selected • The complete cluster-address is produced • Ghosts are removed • Cluster selection is performed to select the highest and the 2nd highest clusters • The sum of the transverse energy of the candidates is calculated INFN Sezione di Bologna

HCAL Selection Crate LVDS 16 Optical Rx INFN Sezione di Bologna

ECAL Selection Crate • The ECAL selection • 2 identical cards, each handling 14 optical and 1 LVDS inputs • No cleaning of copies • No second highest then no ghost cleaning • No SumET produced • Highest cluster from one board goes to the 2nd for the final selection INFN Sezione di Bologna

Hadron Master INFN Sezione di Bologna

The AM Sorter INFN Sezione di Bologna

Sorter Logic Processor Logic FPGA LVDS Parallel VME Interface Auxiliary Electronics ECS Interface Optical Interface INFN Sezione di Bologna

Sorter Logic. Tests Pattern Generator 821-bits Input Channels To the Logic Analyzer 1st max 2nd max sumET INFN Sezione di Bologna

Tx Tx Tx Tx Tx Tx Tx Tx The Selection Board Functional Blocks • Functional Blocks to be tested • Sorter • Optical Input Interface • ECS Interface and Timing • LVDS Output Interface READY To be built in 2003 ECS TTCRx 80m Optical Cables 8 Single Channel Optical Tx Optical Interface To be built in 2002 INFN Sezione di Bologna