Understanding AD7626 LVDS Interface for Synchronous Data and Clock Outputs

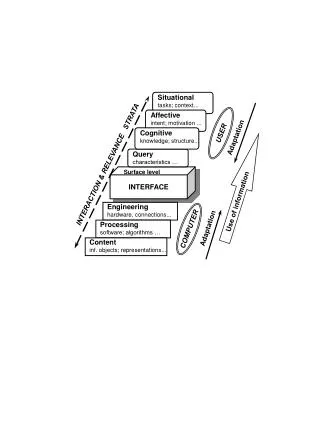

This document explains the operation of the AD7626 interface using LVDS signals for synchronous data (D+/D-) and clock (CLK+/CLK-) outputs. It details the timing constraints defined by tMSB and tCLKL that establish the quiet window for data acquisition during clock burst operations. tMSB denotes the minimum time after the CNV rising edge until the conversion data is ready, while tCLKL ensures completed clocking of current results before new conversions. Following these parameters ensures accurate and effective data retrieval in the system.

Understanding AD7626 LVDS Interface for Synchronous Data and Clock Outputs

E N D

Presentation Transcript

AD7626 Interface

AD7626 Interface - LVDS Use DCO+/- and D+/- as synchronous LVDS data and clock outputs tMSB and tCLKL set the limits for the CLK+/- quiet window

ECHO CLOCK MODE-Creating Burst CLK+/- , tMSB • D+/- is Invalid in the CLK+/- Quiet Window – Highlighted in Yellow • The quiet window is effectively set by tMSB and tCLKL • tMSB is the min time from the CNV rising edge until that conversion data is ready to be clocked out – i.e. once tMSB elapses a burst of 16 CLK+/- may be applied for data acquisition • D+/- is output synchronous to DCO+/-

ECHO CLOCK MODE-Creating Burst CLK+/- , tCLKL • The other limit for the quiet window is set by tCLKL • tCLKL timing spec ensures that you have finished clocking the current conversion result prior to the next result being ready internally in the device i.e. you’re not clock results from two different conversions • For the same data result – tMSB and tCLKL are referenced from consecutive CNV rising edges