Computer Arithmetic Lecture 8

E N D

Presentation Transcript

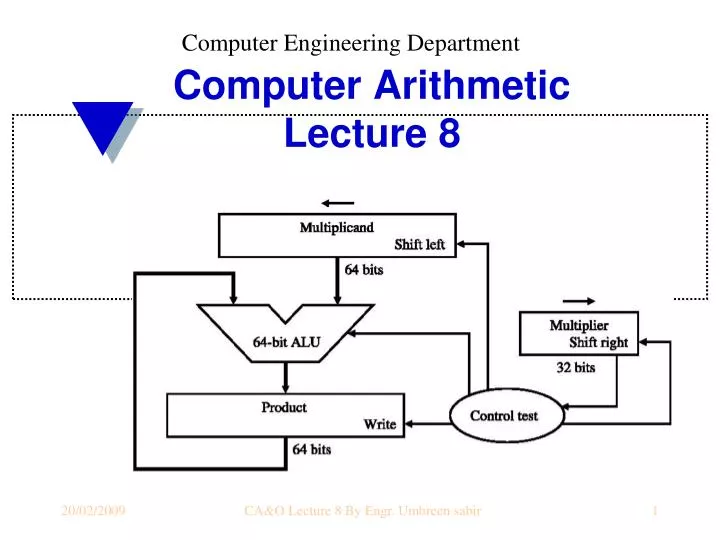

Computer Engineering Department Computer ArithmeticLecture 8 CA&O Lecture 8 By Engr. Umbreen sabir

Number Representation • Binary numbers (base 2) - integers 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 . . . in decimal from 0 to 2n-1 for n bits • MIPS represents numbers as 32-bit constants. 0 ten is in MIPS 0000 0000 0000 0000 0000 0000 0000 0000two • Bit 31 (most significant bit) Bit 3 Bit 0 Thus the largest (unsigned) number is 1111 1111 1111 1111 1111 1111 1111 1111two or 4,294,967,295 ten = 232 -1 CA&O Lecture 8 By Engr. Umbreen sabir

Number Representation • Bits are just bits (have no inherent meaning) conventions define the relationships between bits and numbers • But numbers can also be signed: if the sign bit is 0 the number is positive, if it is 1 the number is negative. • Thus the signed number 1111 1111 1111 1111 1111 1111 1111 1111two is -1ten • With 32 bits the range of integers becomes –231 (-2,147,483,648) is 1000 0000 0000 0000 0000 0000 0000 0000two to 231-1 (2,147,483,647) • Computers use the two’s complement to represent the Xsigned number as (x31 -231)+(x30 230)+…+(x1 21)+(x0 20) CA&O Lecture 8 By Engr. Umbreen sabir

MIPS Representations • 32-bit signed numbers (2’s complement): 0000 0000 0000 0000 0000 0000 0000 0011two = 3ten 1111 1111 1111 1111 1111 1111 1111 1101two = -3ten 0000 0000 0000 0000 0000 0000 0000 0000two = 3ten -3ten = 0 • To get the two’s complement all0s become 1s, and all 1s become 0s, then a 1 is added • Converting n-bit numbers into numbers with more than n bits: • MIPS 16-bit immediate gets converted to 32 bits for arithmetic • copy the most significant bit (the sign bit) into the other bits0010 -> 0000 0010 1010 -> 1111 1010 CA&O Lecture 8 By Engr. Umbreen sabir

MIPS Representations • Exercise:what is the decimal’s equivalent of the two’s complement 1111 1111 1111 1111 1111 1110 0000 1100two • We negate first 0000 0000 0000 0000 0000 0001 1111 0011two 1 0000 0000 0000 0000 0000 0001 1111 0100two • Then we apply the formula (x31 -231)+(x30 230)+…+(x1 21)+(x0 20) 128 + 127 + 126 + 125 + 124 + 122 = =256+128+64+32+16+4=500 CA&O Lecture 8 By Engr. Umbreen sabir

Number Representation • Of course, it gets more complicated • storage locations (e.g., register file words) are finite, so have to worry about overflow (i.e., when the number is too big to fit into 32 bits) • have to be able to represent negative numbers, e.g., how do we specify -8 in • addi $sp, $sp, -8 #$sp = $sp - 8 • real systems have to provide for more than just integers, e.g., fractions and real numbers (and floating point) CA&O Lecture 8 By Engr. Umbreen sabir

0 rs rt rd 0 42 Sign bit 31 magnitude bits Sign bit 10 rs rt constant 11 constant More instructions • Since MIPS uses signed arithmetic, we need “unsigned” versions of operations such as • slt • slti • sltiu • The result of slt and sltu when comparing registers will be different when the most significant bit is 1 CA&O Lecture 8 By Engr. Umbreen sabir

31 25 20 15 5 0 R-type: op Rs Rt Rd funct I-Type: op Rs Rt MIPS Arithmetic and Logic Instructions Immed 16 INST op funct ADDI 001000 xx addiu 001001 xx SLTI 001010 xx sltiu 001011 xx ANDI 001100 xx ORI 001101 xx XORI 001110 xx LUI 001111 xx INST op funct ADD 000000 100000 addu 000000 100001 SUB 000000 100010 subu 000000 100011 AND 000000 100100 OR 000000 100101 XOR 000000 100110 NOR 000000 100111 INST op funct 000000 101000 000000 101001 SLT 000000 101010 sltu 000000 101011 000000 101100 CA&O Lecture 8 By Engr. Umbreen sabir

Addition and Subtraction • Addition is done by carrying 1s to the left 00… 00100 (410) +00… 00100 (410) 00… 01000 (810) • Subtraction is like addition with Two's complement of the second number 00… 00100 (410) - 00… 00011 (310) 00… 00100 (410) + 11… 11101(-310)00… 00001 (110) CA&O Lecture 8 By Engr. Umbreen sabir

Overflow • Adding two numbers of different sign does not yield an overflow • Subtracting operands of same sign does not yield an overflow • Overflow (when number of available bits is not sufficient – addition causes carry out of MSB and subtraction causesa borrow into MSB) Examples of overflow: • A+B<0 (when A,B0); • A+B0 (when A,B<0) • A-B<0 when A0, B<0 • A-B0 when A<0, B0 CA&O Lecture 8 By Engr. Umbreen sabir

MIPS Instructions • Sign extend - addiu, sltiu • Zero extend - lbu • No overflow detected - addu,subu,addiu,sltu,sltiu because unsigned numbers are used for addresses CA&O Lecture 8 By Engr. Umbreen sabir

Overflow Detection and Effects • Some instructions (add, addi, sub) detect overflow and cause an interrupt (exception) • When an overflow interrupt occurs control jumps to predefined memory address for exceptions • Address of instruction causing the overflow is saved for possible resumption. The offending address is stored in the exception program counter$epc (not part of the Register File) • To debug the program, the contents of this register can be moved to a general purpose register “move from system control” (R-Type operation) mfc0 $k1, $epc #$k1=$epc $k0, $k1 OS-reserved registers in Register File • After debugging, and restoring registers, control can return with a jump to the OS-reserved register • jr $k1 CA&O Lecture 8 By Engr. Umbreen sabir

Examples • Find the shortest sequence of instructions to determine if there is a carry-out from the addition of $t3 and $t4. Place 0s in $t2 if carry-out is 0 and 1s in $t2 if carry-out is 1. addu $t2, $t3, $t4 sltu $t2, $t2, $t4 • or addu $t2, $t3, $t4 sltu $t2, $t2, $t3 • Find the shortest sequence of instructions to perform double precision (64-bit) integer addition. Assume one 2’s complement integer is in registers $t4 and $t5 and another in registers $t6 and $t7. The sum is to be placed in registers $t2 and $t3. Most significant word in even-numbered registers. CA&O Lecture 8 By Engr. Umbreen sabir

Example -continued • If no overflow detection is required addu $t3, $t5, $t7 (least signif. 32 bits) sltu $t2, $t3, $t5 #$t2 holds 0s addu $t2, $t2, $t4 addu $t2, $t2, $t6 • If overflow detection is needed addu $t3, $t5, $t7 (least signif. 32 bits) sltu $t2, $t3, $t5 #$t2 holds 0s add $t2, $t2, $t4 add $t2, $t2, $t6 (or add $t2, $t4, $t6) CA&O Lecture 8 By Engr. Umbreen sabir

operation a•b a+b Arithmetic Logic Unit (ALU) • It has four building blocks • The device that performs the computer arithmetic and logic operations • For logic operations only CA&O Lecture 8 By Engr. Umbreen sabir

carry_in a + Sum b carry_out 1-bit Binary Adder Sum = Σminterms = a’b’c + a’bc’ + ab’c’ +a’bc’ carry_out = ab+ac+bc CA&O Lecture 8 By Engr. Umbreen sabir

CarryIn operation a • b a &b, a|b, a+b, 0 3 1-bit Binary Adder • carry_out = a • b+a • carryIn+b • carryIn • is implemented by the gates • The 1-bit ALU with 0 is implemented with the gates CA&O Lecture 8 By Engr. Umbreen sabir

Modifying the ALU Cell for slt Subtraction is same as adding negative b thus Binvert goes Hi, and CarryIn is 1 Less Set Overflow detection Overflow This is the MSB ALU Cell CA&O Lecture 8 By Engr. Umbreen sabir

O O O Bininvert Operation CarryIn Modifying the ALU for slt • First perform a subtraction • Make the result 1 if the subtraction yields a negative result • Make the result 0 if the subtraction yields a positive result Set Overflow CA&O Lecture 8 By Engr. Umbreen sabir

Bnegate Operation Modifying the ALU for beq Output Zero goes Hi for equality CA&O Lecture 8 By Engr. Umbreen sabir