Understanding Hardware Description Languages for Simulation and Design

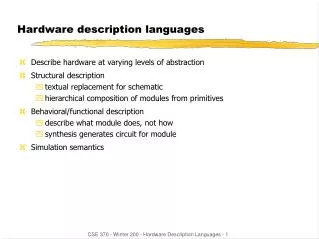

This document provides a comprehensive overview of Hardware Description Languages (HDLs) used in hardware design. It distinguishes between synthesis, where Application-Specific Integrated Circuits (ASICs) or Field Programmable Gate Arrays (FPGAs) are manufactured, and simulation, which focuses on functionality checks. Key topics include procedural versus structural design, interconnection of components, module instantiation, and the importance of I/O ports. Examples illustrate the creation of testbenches that generate input stimuli and monitor outputs, ensuring that simulations accurately reflect real-world behavior.

Understanding Hardware Description Languages for Simulation and Design

E N D

Presentation Transcript

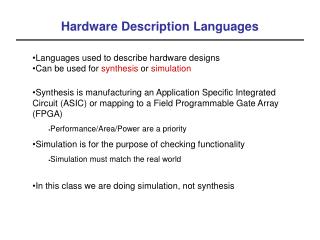

Hardware Description Languages • Languages used to describe hardware designs • Can be used for synthesis or simulation • Synthesis is manufacturing an Application Specific Integrated Circuit (ASIC) or mapping to a Field Programmable Gate Array (FPGA) • Performance/Area/Power are a priority • Simulation is for the purpose of checking functionality • Simulation must match the real world • In this class we are doing simulation, not synthesis

a + b out d + e Hardware Design Procedural Design vs. Structural Design c = a + b f = d + e if (g) out = c; else out = f; • Procedural design describes functionality as a sequence of steps. • Structural design describes an interconnection of components. g

Structural Description, Modules module T_FF (q, clock, reset); . . . . endmodule • Represents a physical component, can be instantiated many times • I/O ports declared at the top • Typically represents a physical component • Can be structurally connected to other components • Cannot be invoked like a function

Instances module ripple_carry_counter(q, clk, reset); output [3:0] q; input clk, reset; //4 instances of the module TFF are created. TFF tff0(q[0],clk, reset); TFF tff1(q[1],q[0], reset); TFF tff2(q[2],q[1], reset); TFF tff3(q[3],q[2], reset); endmodule module TFF(q, clk, reset); output q; input clk, reset; wire d; DFF dff0(q, d, clk, reset); not n1(d, q); endmodule • TFF is instantated within ripple_carry_counter • DFF and not are instantiated within TFF • Structural interconnect is established through instantiation

Testbench (Stimulus Block) // Control the reset initial begin reset = 1'b1; #15 reset = 1'b0; #180 reset = 1'b1; #10 reset = 1'b0; #20 $stop; end // Monitor the outputs initial $monitor($time, " Output q = %d", q); endmodule module stimulus; reg clk; reg reset; wire[3:0] q; // instantiate the design block ripple_carry_counter r1(q, clk, reset); // Control the clock initial clk = 1'b0; always #5 clk = ~clk; • The testbench generates the input stimulus • Observation of data is often included in the testbench