EL310 Hardware Description Languages Spring 20 14

70 likes | 223 Vues

EL310 Hardware Description Languages Spring 20 14. Instructor: Ilker Hamzaoglu Teaching Assistants Ercan Kalalı, Hasan Azgın Web Site: http://people.sabanciuniv.edu/~hamzaoglu/el310/el310.htm. Course Schedule. EL 310 4.00 HW Description Languages M 2 :40 pm - 4 :30 pm F ENS L056

EL310 Hardware Description Languages Spring 20 14

E N D

Presentation Transcript

EL310 Hardware Description LanguagesSpring 2014 • Instructor: Ilker Hamzaoglu • Teaching Assistants Ercan Kalalı, Hasan Azgın • Web Site:http://people.sabanciuniv.edu/~hamzaoglu/el310/el310.htm

Course Schedule • EL 310 4.00 HW Description Languages M2:40 pm - 4:30 pm FENS L056 T2:40pm - 4:30 pm FENS G015 • EL 310L 0.00 HW Desc. Lang. Lab. R6:40 pm - 7:30 pm FASS 1081

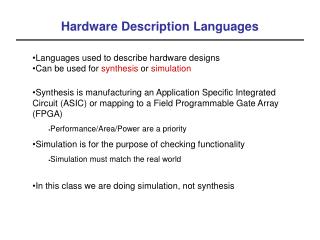

Course Description • This course introduces modeling digital circuits using Hardware Description Languages (HDL). It then introduces Verilog HDL and covers behavioral modeling and verification of digital circuits using Verilog HDL. It then covers RTL modeling with Verilog and logic synthesis to standard cell libraries and FPGAs. • In this course, students will also gain practical design experience by using Mentor Graphics Modelsim, Xilinx XST and Xilinx ISE CAD tools to design and implement several digital circuits.

References • Lecture Slides • Textbooks • A Verilog HDL Primer, Jayaram Bhasker, Star Galaxy Publishing, Third Edition, 2005 • Verilog HDL Synthesis: A Practical Primer, Jayaram Bhasker, Star Galaxy Publishing, 1998

Reference Books • HDL Chip Design: A Practical Guide for Designing, Synthesizing and Simulating ASICs and FPGAs Using VHDL or Verilog, Douglas J. Smith, Doone Publications, 1998 • Verilog HDL: A Guide to Digital Design and Synthesis, Samir Palnitkar, Prentice Hall, Second Edition, 2003 • Real World FPGA Design with Verilog, Ken Coffman, Prentice Hall, 2000 • Advanced FPGA Design, Steve Kilts, Wiley-IEEE Press, 2007

Tentative Schedule • Introduction • Digital Design with Verilog • Verilog Language Elements • Gate-Level Modeling with Verilog • Behavioral Modeling with Verilog • Testbench Design with Verilog • Logic Synthesis, Standard Cell Libraries • Field Programmable Gate Arrays (FPGA) • RTL Modeling with Verilog • Verilog RTL Model Optimizations • Design Verification

Grading • Lab Assignments (4) 40% (Lab1 5%, Lab2 10%, Lab3 10%, Lab4 15%) • Midterm Exam 30% • Final Exam 30% • Midterm exam will be on Tuesday, April 1. • Students will work in groups of two for the lab assignments. • Cheating in the lab assignments and exams is not allowed. It will be strongly penalized.