Advanced Time Synchronization and Data Transmission with EtherBone and WHISBONE Interfaces

This document provides a comprehensive overview of the EtherBone and WHISBONE interfaces as implemented in FPGA designs, specifically focusing on their role in time synchronization and data transmission. It explores the integration of PTP (Precision Time Protocol) for high-accuracy timing, features of SFP (Small Form-factor Pluggable) modules, and FMC (FPGA Mezzanine Card) integration. Additionally, it discusses the use of external PHY and MAC interfaces, along with control mechanisms via EEPROM and I2C protocols. Example designs and specifications illustrate practical applications in node development.

Advanced Time Synchronization and Data Transmission with EtherBone and WHISBONE Interfaces

E N D

Presentation Transcript

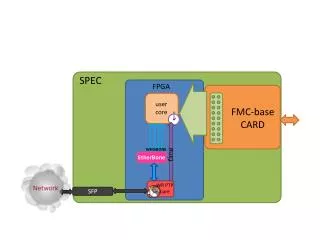

SPEC FPGA user core WHISBONE time time EtherBone WR PTP core SFP FMC-base CARD

SPEC FPGA WR Node Device user core time WHISBONE EtherBone WR PTPcore SFP FMC-base CARD

source Tx Ethernet Rx WR PTP Core external PHY MAC I/F sink pipelined WB Slave I/F 1-PPS Timecode frequency CLKREF CLKDMTD adjust external oscillators WR Node IP Core timing I/F EEPROM I2C control/status pins

source Tx Ethernet Rx WR PTP Core external PHY MAC I/F sink pipelined WB Slave I/F 1-PPS Timecode frequency CLKREF CLKDMTD adjust external oscillators WR Node IP Core timing I/F EEPROM I2C control/status pins SPEC FPGA WR Node Device user core time WHISBONE Example WR Node Design EtherBone WR PTPcore SFP FMC-base CARD

source Tx Ethernet Rx external PHY MAC I/F WR PTP Core sink pipelined WB Slave I/F 1-PPS Timecode frequency CLKREF CLKDMTD adjust external oscillators WR Node IP Core timing I/F EEPROM I2C control/status pins Example WR Node Design SPEC FPGA WR Node Device user core time WHISBONE EtherBone WR PTP core SFP FMC-base CARD