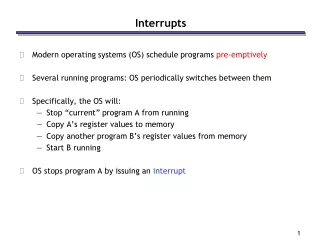

Interrupts

Interrupts. A Course in Microprocessor Electrical Engineering Dept. University of Indonesia. Chapter Objectives:. Explain the interrupt structure of the Intel family of microprocessors Explain the operation of software interrupt instructions INT, INTO, INT 3, and BOUND

Interrupts

E N D

Presentation Transcript

Interrupts A Course in Microprocessor Electrical Engineering Dept. University of Indonesia

Chapter Objectives: • Explain the interrupt structure of the Intel family of microprocessors • Explain the operation of software interrupt instructions INT, INTO, INT 3, and BOUND • Explain how the interrupt enable flag bit (IF) modifies the interrupt structure • Describe the function of the trap interrupt flag bit (TF) and the operation of trap-generated tracing • Develop interrupt service procedures that control lower speed external peripheral devices • Expand the interrupt structure of the microprocessor using the 8259A programmable interrupt controller and other techniques • Explain the purpose and operation of a real_time clock

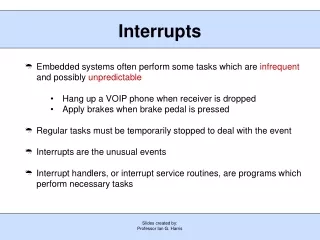

Basic Interrupt Processing • The Purpose of Interrupts • An interrupt is a hardware-or software-initiated call that interrupts the currently executing program at any point and calls a procedure. The procedure is called by the interrupt handler or an interrupt service procedure. • Interrups are useful when an I/O device needs to be serviced only occasionally at low data transfer rates • Fig, 11-1 shows a time line that indicates a typist typing data on a keyboard, a printer removing data from the memory, and a program executing

Basic Interrupt Processing (cont’d) • Interrupts • the interrupts of the entire Intel family of microprocessor include : • two hardware pins that request interrupts (INTR and NMI) and one hardware pin (INTA) that acknowledges the interrupt request through INTR. • Software interrupts INT,INTO,INT 3, and BOUND • Two flag bits, IF(interrupt flag) and TF (trap flag), are used with the interrupt structure and a special return instruction IRET (or IRETD in the 80386, 80486, or Pentium/Pentium Pro)

Basic Interrupt Processing (cont’d) • Interrupts Vectors • the interrpt vector table is located in the first 1,024 bytes of memory at addresses 000000H-0003FFH • it contains 256 different 4-byte interrupt vectors • an interrupt vector contains the address (segment and offset) of interrupt service procedure. • Fig. 11-2 illustrates the interrupt vector table for the microprocessor

Basic Interrupt Processing (cont’d) • The Operation of a Real Mode Interrupt • When the microprocessor completes executing the current instruction, it determines whether an interrupt is active by checking (1) instruction executions (2) single-step (3) NMI (4) coprocessor segment overrun (5) INTR (6) INT instruction in the order presented

Basic Interrupt Processing (cont’d) • If one or more of these interrupt conditions are present, the following sequence of events occurs: 1. The contents of the flag register aew pushed onto the stack. 2. Both theinterrupt(IF) and trap(TF) flags are cleared. Tjis disables the INTR pin and also the trap or single-step feature. 3. The contens of code segment register(CS) are pushed onto the stack. 4. The contens of the instruction pointer(IP) are pushed onto the stack. 5. The interrupt vector contents are fetched and placed into both IP and CS so that the next instruction executes at the interrupt service procedure addressed by the vector.

Basic Interrupt Processing (cont’d) • Operation of a Protected Mode Interrupt • In protected mode, interrupts reference the interrupt descriptor table (IDT) that contains 256 interrupt descriptors. Each interrupt descriptor contains a segment selector and a 32-bit offset address. Fig. 11-3 shows the contents of the interrupt descriptor. • Other than the IDT and interrupt descriptors, the protected mode interrupt functions like the real mode interrupt • The instructions for return is using IRET or IRETD

Basic Interrupt Processing (cont’d) • Interrupt Flag Bits • The interrupt flag(IF) and the trap flag(TF) are both cleared after the contents of the flag register are stacked during an interrupt (see Fig. 11-4). • See Example 11-1 and 11-2 • Storing an Interrupt Vector in the Vector Table • In order to install an interrupt vector ( a hook), the assembler must address absolute memory. • Fig. 11-4 show how a new vector is added to the interrupt vector table by using the assembler and a DOS function call.

Hardware Interrupts • The microprocessor has two hardware interrupt inputs: non-maskable interrupt (NMI) and interrupt request(INTR). • Fig. 11-5 shows the three user interrupt connection on the microprocessor.(see also Fig. 11-8) • The non-maskable interrupt input (NMI) calls the procedure whose address is stored at interrupt vector type number 2. This input is positive-edge triggered.

Hardware Interrupts(cont’d) • The INTR pin is not internally decoded as is the NMI pin. Instead, INTA is used to apply the interrupt vector type number to data bus connections D0-D7 during INTA pulse.(See Fig. 11-9,11-10, and 11-11). • The 82C55 Keyboard Interrupt • Fig. 11-12 illustrates the interconnection of the 82C55 with microprocessor and the keyboard. • Example 11-5 illustrates the interrupt service procedure for the keyboard .

Expanding The Interrupt Structure • This text covers three of the more common methods of expanding the interrupt structure of the microprocessor • Using the 74ALS244 to Expand • See Fig. 11-13 • Table 11-1 shows the interrupt vector used by a single interrupt request input. • Daisy-Chained Interrupt • See Fig. 11-14 • 8259A Programmable Interrupt Controller • See Fig. 11-15,11-16,11-17, and 11-18

8259A Programmable Interrupt Controller • The 8259A programmable interrupt controller (PIC) adds at least eight interrupt inputs to the microprocessor. If more interrupts are needed, this device can be cascaded to provided up to 64 interrupt inputs • General Description of the 8259a • See Fig. 11-15 shows the pin-out of the 8259A • Connecting a Single 8259A • See Fig. 11-16 shows a single 8259A connected to the 8086 microprocessor

8259A Programmable Interrupt Controller(cont’d) • Cascading Multiple 8259As • See Fig. 11-17 shows two 8259As connected to the 80386SX microprocessor in a way that is often found in the AT-style computer, which has two 8259As for interrupts. • Programming the 8259A • Programming the 8259A is a two-step process, First, a series of initialization command words (ICWs) are sent to the 8259A; then a series of operation command words (OCWs) are sent.

8259A Programmable Interrupt Controller(cont’d) • The 8259A contains three status registers: IMR (interrupt mask register), ISR (in-service register), and IRR (interrupt request register) (see Fig. 11-20). • See 8259A Programming Example on page 455- 462

Real-Time Clock • A real-time clock is used to keep time in real-time. In most cases, time is stored in either binary or BCD form in several memory locations. • Fig. 11-26 illustrates a simple circuit that uses the 60 Hz AC power line to generate a periodic interrupt request signal for the NMI interrupt input pin. See also Example 11-14.