Finite State Machines

Finite State Machines. Lecture L5.1 Mealy and Moore Machines. init. Combinational Network. s(t+1). s(t). State Register. next state. present state. x(t). present input. present output. clk. z(t). Canonical Sequential Network. init. C1. C2. s(t+1). State Register.

Finite State Machines

E N D

Presentation Transcript

Finite State Machines Lecture L5.1 Mealy and Moore Machines

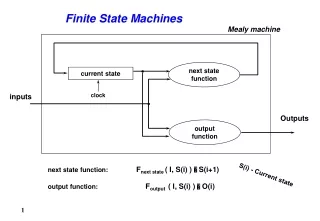

init Combinational Network s(t+1) s(t) State Register next state present state x(t) present input present output clk z(t) Canonical Sequential Network

init C1 C2 s(t+1) State Register next state s(t) z(t) present state x(t) present input clk Mealy Machine

init C2 C1 z(t) s(t+1) State Register next state s(t) present state x(t) present input clk Moore Machine

VHDLCanonical Sequential Network init Combinational Network s(t+1) s(t) State Register next state present state x(t) present input process(clk, init) present output clk z(t) process(present_state, x)

VHDLMealy Machine process(present_state, x) init C1 C2 s(t+1) State Register next state s(t) z(t) present state x(t) present input process(present_state, x) clk process(clk, init)

VHDLMoore Machine init C2 C1 z(t) s(t+1) State Register next state s(t) present state x(t) present input process(present_state, x) process(present_state) clk process(clk, init)

ExampleDetect input sequence 1101 fsm din clk dout clr din dout 1 0 1 1 0 1 1 0 1 0 0 1 1 0 1 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 1 0

Easy Solution:Use Shift Register dout 1 0 1 1 din Q0 Q1 Q2 Q3 D Q D Q D Q D Q CLK !Q CLK !Q CLK !Q CLK !Q CLK

0 1 1 0 0 1 CLR 0 1 0 1 More General: Use State DiagramDetect input sequence 1101 S1 0 S0 0 S11 0 S1101 1 S110 0

fsm.vhd fsm din clk dout clr

S1 0 0 1 1 S0 0 0 S11 0 0 CLR 1 0 1 0 S1101 1 S110 0 1 fsm.vhd

fsm.vhd S1 0 0 1 1 S0 0 0 S11 0 0 CLR 1 0 1 0 S1101 1 S110 0 1

fsmx.vhd LD1 din fsm SW1 dout clr LD8 bn IBUFG clk BTN4 clk_pulse fsmx mclk clkdiv

clk_pulse entity entity clk_pulse is port ( BTN4, cclk, clr: in std_logic; clk: out std_logic ); end clk_pulse; cclk clr BTN4 clk_pulse clk

clk BTN4 delay1 delay2 delay3 cclk clk_pulse

clk BTN4 delay1 delay2 delay3 cclk BTN4 clk

clk_pulse architecture architecture clk_pulse_arch of clk_pulse is signal delay1, delay2, delay3: std_logic; begin process(clk, clr) begin if clr = '1' then delay1 <= '0'; delay2 <= '0'; delay3 <= '0'; elsif clk'event and clk='1' then delay1 <= BTN4; delay2 <= delay1; delay3 <= delay2; end if; end process; clk <= delay1 and delay2 and (not delay3); end clk_pulse_arch ;

fsmx.vhd entity fsmx is port( mclk : in STD_LOGIC; bn : in STD_LOGIC; SW1 : in STD_LOGIC; BTN4 : in STD_LOGIC; led: out std_logic; ldg : out STD_LOGIC; LD : out STD_LOGIC_VECTOR(1 to 2) ); end fsmx;

fsmx.vhd component clk_pulse port( BTN4 : in std_logic; cclk : in std_logic; clr : in std_logic; clk : out std_logic); end component; signal clr, clk, cclk, bnbuf: std_logic; signal clkdiv: std_logic_vector(23 downto 0);

fsmx.vhd U0: clk_pulse port map (BTN4 => BTN4, cclk => cclk, clr =>clr, clk => clk); U1: fsm port map (clr =>clr, clk => clk, din => SW1, dout => LD(2)); LD(1) <= SW1;

Verilog fsmv.v // Finite state machine -- detect sequence 1101 module fsm(clk,clr,din,dout); input clk, clr, din; output dout; reg dout; reg[4:0] present_state, next_state; parameter S0 = 5'b00001, S1 = 5'b00010, S11 = 5'b00100, S110 = 5'b01000, S1101 = 5'b10000; always @(posedge clk orposedge clr) begin if (clr == 1) present_state <= S0; else present_state <= next_state; end

S1 0 0 1 1 S0 0 0 S11 0 0 CLR 1 0 1 0 S1101 1 S110 0 1 always @(present_state or din) begin case(present_state) S0: if(din == 1) next_state <= S1; else next_state <= S0; S1: if(din == 1) next_state <= S11; else next_state <= S0; S11: if(din == 0) next_state <= S110; else next_state <= S11; S110: if(din == 1) next_state <= S1101; else next_state <= S0; S1101: if(din == 1) next_state <= S11; else next_state <= S0; default next_state <= S0; endcase end fsmv.v (cont.)

fsmv.v (cont.) always @(present_state) begin if(present_state == S1101) dout = 1; else dout = 0; end endmodule

module clk_pulse(BTN4, cclk, clr, clk); input cclk, clr, BTN4; output clk; wire clk; reg delay1, delay2, delay3; always @(posedge cclk orposedge clr) begin if (clr == 1) begin delay1 <= 0; delay2 <= 0; delay3 <= 0; end else begin delay1 <= BTN4; delay2 <= delay1; delay3 <= delay2; end end assign clk = delay1 & delay2 & (!delay3); endmodule clk_pulse.v

Top-level design fsmvx.v module fsmx(mclk, bn, SW1, BTN4, led, ldg, LD); input mclk, bn, SW1, BTN4; output ldg, led; output [1:2] LD; wire [1:2] LD; wire clr, cclk, bnbuf; reg [26:0] clkdiv; IBUFG U00 (.I (bn), .O (bnbuf)); assign led = bnbuf; assign clr = bnbuf; assign ldg = 1; // enable 74HC373 latch

fsmvx.v (cont.) // Divide the master clock (50Mhz) always @(posedge mclk) begin clkdiv <= clkdiv + 1; end assign cclk = clkdiv[17]; // 190 Hz clk_pulse U0(.BTN4(BTN4),.cclk(cclk),.clr(clr),.clk(clk)); fsm U1(.din(SW1),.dout(LD[2]),.clr(clr),.clk(clk)); assign LD[1] = SW1; endmodule