Interactive Visual Response System (VRS) for Tic-Tac-Toe on FPGA

This project aims to develop an interactive Visual Response System (VRS) utilizing an FPGA to create a simple Tic-Tac-Toe game. By integrating a UART interface to communicate between the system and the user's PC via the internet, users can input commands using Minicom. The system dynamically allocates images for the game's display, utilizing parallel processing capabilities of FPGAs to efficiently manage game states and responses. The project explores real-time updates to provide visual feedback on the monitor, enhancing user interaction.

Interactive Visual Response System (VRS) for Tic-Tac-Toe on FPGA

E N D

Presentation Transcript

Simply Gaming Final Project Project Leader: PJ Acevedo pjacevedo@msn.com Fall 2009

ML507 Development Board 1 3 UART FPGA 2 DVI 4

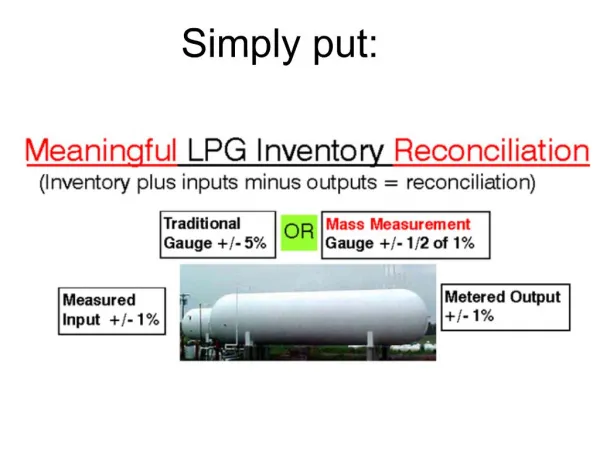

Project Idea • Create an interactive Visual Response System(VRS) • Use “minicom” as an input to system • Update “echo.c” to provide output to monitor • Connect from any remote PC via the internet • Motivation stems from the ability of FPGAs to process data in parallel thus giving the ability to apply changes to different data blocks concurrently • Result will be to create a simple game such as Tic-Tac-Toe to explore the above possibilities 10/31/09

Visual Template DVI Interface 10/31/09

Initial Concerns • Not enough memory to store the four fixed frames • Monitor refresh needs to be faster than 60Hz which is a typical monitor refresh rate • System might be too slow when refreshing squares 10/31/09

Gantt Chart • Board Layout • Create dimensions of game frame by 10/31 • Minicom Interface • Basic read/write subroutines by 10/31 • Monitor Interface • Basic draw subroutines by 10/31 • APU Interface • Game engine and project integration by 11/14 • Top-Level Integration • Integrate all interfaces into a complete system by 11/28 12/05/09

System Block Diagram ml507 Virtex 5 apu PPC 440 DDR memory video game_ engine uart minicom 12/05/09

Visual Template DVI Interface • VGA MONITOR • Break up display into eight frames • Place dividers in between frames • Refresh the frames as needed and leave the rest unchanged • STORED MEMORY • The initial idea of having a stored image in DDR was changed. • As a new frame was needed, the PPC440 dynamically allocated the image where needed 10/31/09

Game Frame Dimensions • Dimensions denoted by meas(s,e) where meas signifies measurement coordinates, s equals starting pixel x/y coordinate and e equals ending pixel x/y coordinate • Outer frame meas(A,G) • Inner vertical frame meas(B,F) • Inner horizontal frame meas(C,E) • Maximum player X/O designator meas(A,D) 12/05/09

Human Input UART Interface • Use Minicom to communicate with system • Command entries: • X 1 1 . : Enter an X in the first row, first column • O 2 2. : Enter an O in the center • M : Display menu • S : Start new game • E : Exit game • Notification of winner will be displayed with a green highlight over the winning choices. 10/31/09

Minicom TerminalUART Interface • Prints Welcome Menu • Display game input options • Signal user of invalid inputs • Provide a restart/terminate option to user Note: This is an actual copy of screen 12/05/09

Game Engine State MachineFPGA Fabric via APU P_EDGE / (IS_FULL = '1', X_STATUS = '1' or O_STATUS= '1') start chk_entry P_EDGE / (IS_FULL = '0', X_STATUS = '1' or O_STATUS= '1') RESET = '0' P_EDGE / (IS_FULL = '0' or IS_FULL = '1') CHOICE= PREV_CHOICE/ IS_REPEAT= '1' DONE= '1' fill_entry CHOICE= X(x,y) or O(x,y) CHOICE /= PREV_CHOICE • Default Outputs and description of signals: • IS_REPEAT <= '0'. Notifies of a repeat of X or O. • IS_FULL <= '0'. Notification if board is full. • X_STATUS <= '0'. Notification if X wins. • O_STATUS <= '0'. Notification if O wins. • DONE <= '0'. Notification if user entry has been processed. 12/05/09

Game Engine HW FPGA Fabric via APU store/127 load/127 game engine choice/1 row/1 col/1 apu done/1 is_full/1 is_repeat/1 x_status/1 o_status/1 • store: 127-bit bus that sends game_engine results to processor • load: 127-bit bus that accepts user game input from processor • choice: Denotes if X or O has been chosen • row: Denotes row of game board • col: Denotes column of game board • done: Tells apu that game_engine is done processing • is_full: Denotes if game board is full • is_repeat: Denotes if user input is a repeat • x_status: Denotes if X has one the game • o_status: Denotes if O has one the game 12/05/09

Final Product • Monitor displays each player in different colors • Monitor gives visual feedback og game winner by highlighting appropriate squares and text prompt at bottom of screen • Minicom provides a user menu and game feedback 12/05/09

NOTES • Use parallelism of FPGA to update Bit Patterns 10/31 • Bit Patterns will contain pre-defined .ppm 10/31 • Changed initial concept of a stored image in DDR and used dynamic creation 11/01 • Used the “apu_inv” hardware from the previous project as the interface between the ppc440 and the game_engine created in the fpga fabric. 11/21 • The game_engine is the brains of the game. It makes all the decisions related to game play. 11/21 • The ppc440 controls communication with the user via the minicom interface using one of its UART peripheral setups. It also controls the visual display via the vga controller. 11/21 10/31/09

Related Research Papers • FPGA RTL View: • http://decibel.ni.com/content/docs/DOC-2172?metc=mtxm4n from National Instruments website by G-Money • Decision Algorithm: • http://www.ddpp.com/DDPP3_mkt/c06samp6.pdf by John F. Wakerly 10/31/09

QUESTIONS Please email me at: pjacevedo@msn.com if you would like more information about my design. Thank you!