DIRECT MAPPING CACHE

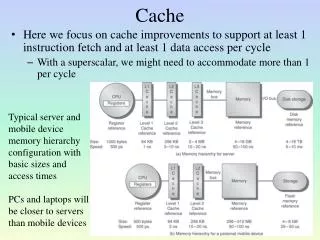

DIRECT MAPPING CACHE. DREAM TEAM 2 Roto, Holiano, Chaka. Block Diagram. Specifications. 4 cache line Each line includes: 4bits tag, 2bits index, 8bits data Only Read or Write is allowed at one time Write Operation Address is decomposed into Tag, Line, Data

DIRECT MAPPING CACHE

E N D

Presentation Transcript

DIRECT MAPPING CACHE DREAM TEAM 2 Roto, Holiano, Chaka

Specifications • 4 cache line • Each line includes: 4bits tag, 2bits index, 8bits data • Only Read or Write is allowed at one time • Write Operation • Address is decomposed into Tag, Line, Data • 2bit lines are used for selecting cache line • Tag and data are written to respected cache line • Read Operation: • 2bit lines are used for selecting cache line • Tag bits are read from the cache line and compared to the input • If the tag is matched, then read outputs data and pulls the status signal up

Work plan • System Design: Roto, Holiano, Chaka • Memory cell and Cache line: Roto • MUX-DEMUX: Holiano • Comparator: Chaka • System Integration: Roto-Holiano-Chaka • Functional Verification: Roto-Holiano • Layout check: Chaka

Tag Read/Write Tdf = 2.1ns Tdr = 2.3 ns

Read hit Read Miss

Read hit Read Miss

System Summary • Frame size in Lambda : 5000.00 x 5000.00 • Length of nets in core : 170751.00 Lambda • Number of Metal layer: 2 • Generated vias in core : 635 • Number of standard cells : 184 • Number of signals in netlist : 336 • Read time: • tdf = 17ns • tdr = 9ns

Conclusion • The system work well and matches the functional specifications • The system is simple, should have more functions • All team have worked well in cooperation • More than 60% of design time is for functional verification • We have successfully designed and implemented a digital system from transistor level to layout