Memory Cache Tracing Exercise Setup Information

Exercise #1 provides setup information for a memory cache tracing exercise involving memory address offsets, cache blocks, indexing tags, and memory content. Followed by Exercise #2 which traces memory access and cache loads using the setup provided.

Memory Cache Tracing Exercise Setup Information

E N D

Presentation Transcript

Direct Map Cache Tracing Exercise

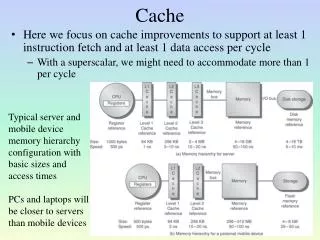

Exercise #1: Setup Information Memory 4GB Offset Offset Block Number Index Tag Memory Address Offset, N = Block Number = 31 N N-1 0 1 Block = 8 bytes N+M-1 31 N N-1 0 Cache 32Bytes Number of Cache Blocks = Cache Index, M = Cache Tag = 1 Block = 8 bytes Cache I

Exercise #2: Tracing Memory Access Memory Content Cache I • Using the given setup, trace the following memory loads: • Load from addresses: 4, 0, 8, 12, 36, 0, 4 • Note that “A”, “B”…. “J” represents word-size data

Exercise #2: Load #1 Tag Index Offset Addresses: 4, 0, 8, 12, 36, 0, 4 00000000000000000000000000 00 100 Address 4 = Cache I

Exercise #2: Load #2 Tag Index Offset Addresses: 4, 0, 8, 12, 36, 0, 4 00000000000000000000000000 00 000 Address 0 = Cache I

Exercise #2: Load #3 Tag Index Offset Addresses: 4, 0, 8, 12, 36, 0, 4 00000000000000000000000000 01 000 Address 8 = Cache I

Exercise #2: Load #4 Tag Index Offset Addresses: 4, 0, 8, 12, 36, 0, 4 00000000000000000000000000 01 100 Address 12 = Cache I

Exercise #2: Load #5 Tag Index Offset Addresses: 4, 0, 8, 12, 36, 0, 4 00000000000000000000000001 00 100 Address 36 = Cache I

Exercise #2: Load #6 Tag Index Offset Addresses: 4, 0, 8, 12, 36, 0, 4 00000000000000000000000000 00 000 Address 0 = Cache I

Exercise #2: Load #7 Tag Index Offset Addresses: 4, 0, 8, 12, 36, 0, 4 00000000000000000000000000 00 100 Address 4 = Cache I