Balancing Rules and Tools in Modern Design Processes

This article discusses the challenges of rule-based design systems in complex modern processes, proposing model-based tools as a solution. It explores the limitations of current rule books, the need for efficient solutions, and compares the benefits of rules versus tools implementations. The text highlights examples from various fields and debates the effectiveness of law-based systems versus ethics-based honor codes. It also delves into the implications of restricted design rules and the potential for improved outcomes through a balanced approach. The importance of adapting to new methodologies and the impact on designers are also addressed.

Balancing Rules and Tools in Modern Design Processes

E N D

Presentation Transcript

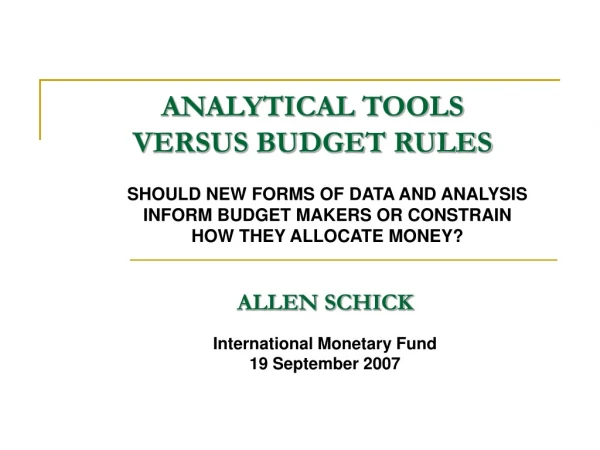

Rules vs. Tools Lou Scheffer. Lars Liebmann, , Riko Radojcic, David White ISPD Austin, March 2006

What’s the problem? • What are designers allowed to design? • Design rules are the traditional solution • But modern processes are very complex • Rule books become huge (>600 pages) • Too much to easily remember and use • Still do not tell enough • Two possible solutions • Restricted rules - ‘Rules’ • Model based design – ‘Tools’

What’s wrong with the current system • In the beginning, there was a rule for contact spacing…

What’s wrong with the current system • Then there were different same-net rules • This was pretty easy to understand

What’s wrong with the current system • Then the spacing started to depend on the number of neighbors > 2 neighbors 0, 1, or 2 Neighbors

What’s wrong with the current system • Now need a rule on what constitutes a neighbor These are officially neighbors

What’s wrong with the current system • So a 3x3 array uniformly needs the ‘big’ rule

What’s wrong with the current system • And some clever designer notices this Now you can use the 2 neighbor rule!

What’s wrong with the current system • But the fab does not think this should be allowed No, you cannot use the 2 neighbor rule!

What’s wrong with the current system • So now there is a rule stating ‘It is not legal to remove the middle via of a 3x3 array in order to use the 2 neighbor rule’ • Hard to check in DRC • Hard to remember • Is this a good use of everyone’s time? • Does it really make a yield difference?

So what could you do? • ‘Rules’ – here is a list of the legal via arrays. You must use one of these. • ‘Tools’ – here is a test that tells which via arrays are manufacturable. Any via array this passes this test is OK. • ‘Extreme tools’ – here is a model that predicts via fail rate in manufacturing. You decide.

Can do this at many levels • Layout • Example : Restricted design rules • Circuit • Example: No dynamic logic • Architecture • Example: Must have latches on block boundaries

Problem not unique to IC design • 3 cases from other fields • One where both approaches are used, with extreme size differences • One where rules are used • One where models are used

Law vs ethics • What is allowed behavior? • Rules based – legal systems • Tools based – honor codes • Specify by laws (info from Wikipedia, USA federal only) • Divided into 50 ‘titles’; each 1 or more printed volumes • Titles may optionally be divided into subtitles, parts, subparts, chapters, and subchapters. • For example, privacy act of 1974 is “Title five, United States Code, section five hundred fifty-two A."

Law vs Ethics • The basic intent of all these laws can be replaced by an ‘honor code’, such as • A cadet will not lie, cheat, steal, or tolerate those who do • Much, much shorter (5 orders of magnitude?) but requires interpretation

Example where rules are the accepted way • Civil engineering – building codes • Detailed code not needed in principle • Quite conservative (6x safety factors) • Reduces the chance of error • Designed to be easy to inspect • Reduces the consequence of error • Big safety factor • Makes sure common failures are addressed • Multiple exits, exit lighting, width of doorways, etc.

Example where models are the rule • Food – both rules and info are possible: • Rule: Eat your vegetables before dessert • Tool: each food lists calories and ingredients; you decide what to eat. • Different people have different tradeoffs • Disclose, then let people decide for themselves

Benefits from restricted rules? • Problem: Even a simple wire is hard to predict • Lithography is a complex operation • Designer draws a polygon • OPC is applied (very non-linear) • Exposure through a complex optical system • Develops a non-linear resist, then etch • Need to add CMP to model vertical dimension • Then need to compute range of variation • Can all be modelled, but it’s not easy

Restricted design rules: Do this • One direction, one width, one spacing, all wires on grid, all empty spaces filled

Tried this as an experiment • Forbid wrong way in router • Wire length only 1% greater • Routability unchanged • 10% more vias • But if this lets you print smaller, it’s a (big) net win!

Implications for Designer For designer/CAD, looks like lots of restrictions • Power routes must be wires in parallel • Wide signal nets must be parallel wires • Delay computation must handle loops • Routers cannot jog – more vias • IP blocks cannot be rotated • Litho folks often phrase this as ‘This is needed, or you won’t get 45 (or 32 or 22 nm…) • Designers don’t believe this for historical reasons • Looks like the fab is saying “Eat your vegetables”

Implications for Fab • Litho is very easy; can be tuned for direction • Illumination andpolarization can be optimized • CMP is very easy • No width effects, small density variations • Can help with non-modelled effects • These are nice for the fab, but designer does not care • Can produce a smaller pitch • Variation can be (much) less • These are things designers value

Political implications • Fab needs to ‘share’ the benefits, e.g. • 90 nm pitch with restricted rules • Smaller variation • Or • 100 nm pitch with arbitrary geometries but larger variation • Then designers could see the benefit, and decide for themselves…

And now our panelists • Each with a different perspective • Lar Liebmann • Litho guy • David White • CMP modeller • Riko Radojcic • User perspective

Questions to keep in mind • Can the average engineer use complex models productively? • Can the EDA tools use these models? • Can the fabs provide these models, keep them updated, and stand behind them? • Won't this keep fabs from making improvements to their process?

More questions • What's the relative importance of time to market and getting the most out of the silicon? • How big is the penalty, or benefit, for using restricted rules? • Of the many problems (litho, CMP, lifetime degradation, etc.) which should be treated by rules and which by models? • Should this be design dependent?