Estimating Wire Length in Block Placement with Opaque Blocks: A Theoretical Study

260 likes | 390 Vues

This study examines wire length estimation algorithms for block placement in CAD applications where opaque blocks can lead to inaccuracies in Half-Perimeter Wire Length (HPWL). By analyzing obstacle-avoiding shortest path lengths, we provide algorithms with competitive time complexity, similar to traditional HPWL methods. Our contributions include reformulating existing theoretical work to fit CAD contexts, proposing minimal wire length calculations for two-pin nets, and identifying bounds for visibility graph paths. Future work will explore routing congestion and multi-pin net handling.

Estimating Wire Length in Block Placement with Opaque Blocks: A Theoretical Study

E N D

Presentation Transcript

A Theoretical Study on Wire Length Estimation Algorithms forPlacement with Opaque Blocks Tan Yan*, Shuting Li Yasuhiro Takashima, Hiroshi Murata The University of Kitakyushu * Now with University of Illinois at Urbana-Champaign

Motivation • “Opaque” blocks makes HPWL inexact • Because of IP blocks, analog blocks, memory module… • Lead to timing violation, unroutable nets…

Motivation—cont’d • Exact wire length estimation for Block Placement • the obstacle-avoiding shortest path length • Time complexity: O(n)? O(n2)? O(nlogn)?... • Time complexity is almost the same as HPWL! • Already proposed in Computational Geometry • However • Not well-known in CAD community • Need interpretation to be applicable to CAD!

Our Contribution • We restate the results in [P.J.de Rezende ’85] & [M.J.Atallah ’91] • Simplify the discussion (with Block Placement notions) • CAD-oriented language • Tailor the theory to fit into Physical Design background

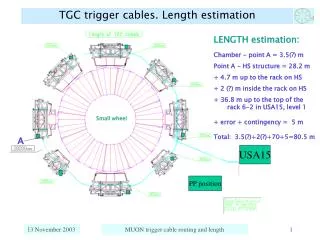

Problem Formulation • Input: • Block location • Pin location (on block boundaries) • ABLR relations * (obtainable from Sequence Pair, etc) • Output: • Rectilinear block-avoiding shortest path length for every 2-pin net • = Minimal Wire Length (MWL)

Assumption • 2-pin net • s on S, t on T • S≠ T • S is left-to T • ys ≤ yt t S T s

Theorem 1 • MWL = HPWL ↔ RU locus of s goes below or through t • Proof omitted

Lemma 2 • There exists an MWL routing inside the AB-region

MWL = shortest path length • Lemma 4: There exists a path (s,t) on the visibility graph that corresponds to an MWL routing. • Only linear number of edges, but still captures MWL!

The overall flow and so on …

Time complexity • M = # of blocks, N = # of nets • Building visibility graph: • O(M logM) • Estimating one net: • O(M) • Total: • O(M logM + NM) • Shortest path on channel graph takes O(NM2)

Use LUT to enhance the speed • No path between two vertices? (a2b2) • Need to judge whether RU locus above t ? • How to find out A & B promptly?

Two lemmas: • Lemma 5: Two vertices s and t on visibility graph. If there is no path between them, then MWL = HPWL • Lemma 6: If t is above s’s RU locus and there exists a shortest path between them, then its length = HPWL. • MWL(a,b) = HPWL • ShortestPath(c,d) = MWL (c,d) = HPWL

Theorem 3 • The MWL of any two vertices on the visibility graph can be obtained by shortest path algorithm: • Shortest path exists, MWL = path length • Otherwise, MWL = HPWL

How it works Lookup table MWL = shortest path length No path! MWL = HPWL And so on…

Time complexity • Building LUT: • O(M2) • Estimating one net: • O(1) • Total: • O(M2+N) • Almost the same as HPWL!

Future works • Integration of routing congestion • Extension to handle multi-pin nets • Application to global router • Experimental study

Thank you! Q & A

Proof of Theorem 1 • MWL = HPWL ↔ RU locus of s goes below or through t

Proof of Lemma 2 • There exists an MWL routing completely inside AB-region

Proof of Lemma 4 • There exists a path p from s to t on HVG that corresponds to an MWL routing.

Proof of Lemma 6 • If t is above s’s RU locus and there exists a shortest path between them, then its length = HPWL.