Double Patterning Technology Friendly Detailed Routing

Double Patterning Technology Friendly Detailed Routing. Minsik Cho, Yongchan Ban, David Z. Pan ECE dept. Univ. of Texas at Austin IBM T. J. Watson Research Center. Outline. Background Why to use Double Patterning? Problem formulation Double Patterning Friendly Detailed Routing

Double Patterning Technology Friendly Detailed Routing

E N D

Presentation Transcript

Double Patterning TechnologyFriendly Detailed Routing Minsik Cho, Yongchan Ban, David Z. Pan ECE dept. Univ. of Texas at Austin IBM T. J. Watson Research Center

Outline • Background • Why to use Double Patterning? • Problem formulation • Double Patterning Friendly Detailed Routing • Layout Decomposition Algorithm • Coloring Path & Shadow Algorithm • Experimental Results • Conclusion

k1: lithography difficulty NA: numerical aperture λ: wavelength of source HP: min. printable half pitch Lithography Challenges in sub 45nm • Higher k1 implies easier manufacturing.

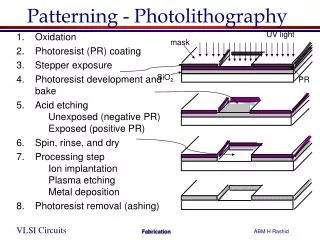

C D E A mindp B Layout Decomposition Mask 2 Mask 1 DOUBLE PATTERNING Stitch • Feature size is still 32nm, but HP is doubled. • 2x mask, 2x litho, 2x etch, and …

Stitch Stitch Challenges in Double Patterning Layout Decomposition • Decomposable layout • Overlay tolerant layout • stitch minimization

C D E E A A D B C B Uncolorable C D E E B A D B C Layout Decomposition vs. 2-coloring E A D A Stitch B C A • Layout decomposition for DPT is more complex than 2-coloring

Complexity of Layout Decomposition • Problem Formulation • Decompose a layout with minimum stitch count • Decomposition approaches • Bipartite graph algorithm, Nikolsky-SPIE’08 • ILP (integer linear programming), Yao-ICCAD’08 • Need support from Physical Synthesis • Industrial effort is first routing, then decomposition • Uncolorable polygon ripup&rerouting long TAT • Needs to solve decomposition and stitch minimization Routing can play a critical role in DPT

Overall Flow Pins , power/ground, clock Color Blockages Update Grid States Route a Wire Color the Routed Path Update Grid States N all wires routed? Y Decomposed Layout • Simultaneous routing and decomposition • No additional step for layout decomposition

A A A D B D B B C Black-colorable Existence of grey-colored objects in the proximity BG Grey-colorable Existence of black-colored objects in the proximity BG BG BG BG BG Uncolorable Existence of grey and black- colored objects in the proximity BG Bicolorable Non-existence of any colored objects in the proximity BG Grid State for DPT • Four possible states for each routing grid using a 2bit variable – small overhead BG

BG BG BG BG BG Penalty for DPT-Unfriendly Path • While finding a path during routing, the following cases along the path are penalized Both cases will introduce a stitch, while coloring the path Stitch cost: α This case will lead to a uncolorable layout Failure: β Some colorable path may have many vias to avoid uncolorable grids Via Via cost: γ • Perform a detailed routing using the A* search • Additional cost modification to find a path

BG BG BG BG BG BG Via BG BG BG BG BG BG Via BG Two vias Cost += 2γ Penalty for DPT-Unfriendly Path Two stitches Cost += 2α Source BG BG Poor decomposability Cost += β Target

BG BG BG BG BG BG BG BG BG BG BG BG BG BG subpath X subpath Y subpath Z BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG Minimum spacing BG BG BG BG Minimum spacing BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG BG Coloring Path & Shadow • Routing Path Coloring • Color Shadow

Experiment Results: Setup • Impletemeted in C++ • Linux on Intel 3.0 Ghz with 16G RAM • Four ASIC blocks scaled from 65nm to 32nm • Two Detailed Routing Algorithms • DR+LD : detailed routing followed by layout decomposition (current industrial practice) • DPFR : proposed work-double patterning friendly detailed routing

Experiment Results: Decomposability • Significantly better decomposability • Reduce the design iteration • Double patterning friendly library design and placement

EXPERIMENT RESULTS: OVERLAY TOLERANCE • Significantly less number of stitches • More robust against overlay error

Experiment Results: Runtime • 3x faster overall design flow • Actual routing is slower (4x), but no separate decomposition step

Conclusion • Double patterning is the forerunner lithography solution for 32/22nm nodes • Double patterning needs supports from CAD • Layout decomposition • Overlay error tolerance • Double patterning technology friendly routing algorithm is proposed • Much more effective than current industrial practice • Reduced turn-around-time