Differences in ISA: RISC vs. CISC Comparison & Benefits

Explore the variances in Instruction Set Architecture (ISA) between RISC and CISC processors, evaluating aspects like instruction length, addressing modes, and operand types. Compare the benefits in terms of speed, production cost, development cost, and flexibility for improvement. Discover examples from Intel, AMD, HP, Motorola, IBM, Apple, and Sun.

Differences in ISA: RISC vs. CISC Comparison & Benefits

E N D

Presentation Transcript

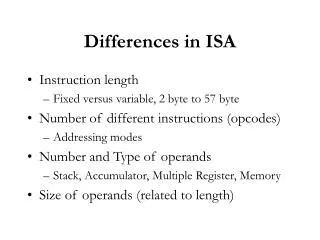

Differences in ISA • Instruction length • Fixed versus variable, 2 byte to 57 byte • Number of different instructions (opcodes) • Addressing modes • Number and Type of operands • Stack, Accumulator, Multiple Register, Memory • Size of operands (related to length)

Number of Instructions • RISC: Reduced instruction set computer • Fewer instructions • Fixed length • Short opcode • CISC: Complex instruction set computer • More instruction • Variable length • Longer opcode

Example: Subtraction C=A-B RISC: LOAD R1, A LOAD R2, B NOT R2, R2 ADD R2, R2, 1 ADD R2, R2, R1 STORE C,R2 CISC: SUBMEM C, A, B

Which is better? • Better in what terms? • Speed • Cost of production • Cost of development • Flexibility for improvement

Better in terms of speed? • CISP: • few instruction • Multiple cycle per instruction • Low cycle time • RISP: • many instruction • one cycle per instruction • High cycle time No clear answer!

Examples for CISC and RISC • CISC • Intel Pentium • AMD • IBM 390 • RISC • HP PA • Motorola, IBM,Apple: PowerPc • Sun Ultra: SPARC