Introduction to Cadence Opus

680 likes | 1.01k Vues

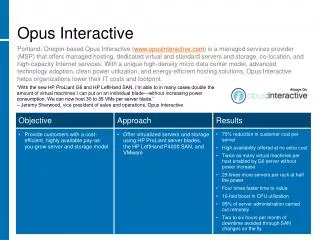

Introduction to Cadence Opus. Digital HDL design Silicon Ensemble. SE-PKS. PKS. Silicon Ensemble. DEF HDL. Floorplanning. Synthesis, Placement. DEF HDL. Floorplanning refinement. Clock Tree Generation. Post Clock Tree Optimization. DEF WDB. Final Routing.

Introduction to Cadence Opus

E N D

Presentation Transcript

Introduction to Cadence Opus Digital HDL design Silicon Ensemble

SE-PKS PKS Silicon Ensemble DEF HDL Floorplanning Synthesis, Placement DEF HDL Floorplanning refinement Clock Tree Generation Post Clock Tree Optimization DEF WDB Final Routing Global Routing and Optimization SPF Parasitic Extraction SI Analysis and Repair WRoute ECO DEF HDL Delay Calculation Verification In-Place Optimization PKS and Silicon Ensemble PKS

Main features • Automatic time budgeting • Interactive floorplan editor • Special power net routing • Productive global and detail placement • One-pass test synthesis • Automatic clock tree synthesis • Productive global and detail routing • Productive design analysis and debug • Full incremental accurate timing analysis • Faster run times and larger design capacity

Constraint application a Automatic generation b c d e f g h i j k l m n Block i Block h 6 ns block target 4 ns block target 10 ns chip target Automatic time budgeting • Automates bottom-up placement and routing • Enables design methodolo-gies that require a bottom-up approach. • Automatically computes lower-level constraints from top constraints. • Slack allocation is based on logic compressibility. • High capacity reduces the number of partitions.

Interactive floorplan editor • Creates the starting floorplan by estimating the required layout area (die size and aspect ratio) • Adjusts the floorplan to accommodate design requirements • Creates the global and detailed routing grids • Creates the I/ O rows • Creates the core rows • Creates sites for corner cells

Special power net routing • Automates creation of rings for common floorplans (rings and stripes) • Automates creation of stripes over standard cell rows. • Makes it easy to edit ring and stripe wires (change width). • Makes it easy to connect and disconnect “everything” to rings (blocks, stripes, rows, I/O rings, and Power Pads).

Global and detail placement • Allows automatic grouping and initial placement of macros, standard cells and IOs • Determines legal placement locations and the site requirements • Anticipates routing requirements by considering the resulting positions of sets of pins that represent nets • Supports netlist-driven placement optimization • Extracts estimated parasitic information for timing critical designs • Reports placement congestion map • Uses same algorithms as PKS logic synthesizer

One-pass test synthesis • Top-down and bottom-up scan insertion • Verilog/VHDL (RTL and/or structural netlists) • Multiple clock domains (on separate chains) • Multiple balanced scan chains • Scan/Nonscan register reporting • Single-pass test synthesis • Full register scan • Multiple scan styles • DFT rule checking • Test mode setup • Shared I/O for test pins

Automatic clock tree synthesis • Constructs an optimized clock tree • Minimizes skew and clock tree insertion delay • Controls user buffer or inverter selection Generates correct syntax for the router • Accepts a placed netlist

Global and detail routing • Creates a global routing plan • Uses the routing grid, GCell grid, netlist view, and the locations of pins and blockages of placed components to create the plan • Creates detail routing for nets, or parts of nets, that have a global routing plan • Uses the routing grid, GCell grid, global routing, and the locations of pins and blockages of placed components to create detail routing • Supports timing-driven optimization • Includes auto search and repair tool

Productive analysis and debug • Critical path analysis • Accurate timing displayed on schematic • Cross-correlation between reports and RTL Timing histograms • Design statistics • Parasitic backannotation • Clock skew analysis • Floorplan verification • Geometry verification

retime D Q D Q critical path! stale data okay CLK CLK unchanged D Q D Q U1 CLK CLK Full incremental timing analysis • Re-times only individual gate • Performs only necessary updates • Much larger design capacity and less memory usage • Converging placement and routing results

Available Documentation • Documentation is available in HTML and PDF formats. • Includes the complete documentation set (User Guides, Command Reference and Application Notes). Netscape is shipped with all Cadence synthesis tools • Subscribe to http://sourcelink.cadence.com for best online help with Cadence tools. • There is a text help feature for sesi. At the sesi prompt, enter: help <command_name> or help <error_code>

Prerequisites to start PKS • Set the Unix environment variables (This solution is site specific!) setenv CDS_INST_DIR /soft/opus/dsmse53 setenv CDS_INSTALL_DIR /soft/opus/dsmse53 setenv PATH $CDS_INST_DIR/tools/bin:$CDS_INST_DIR/tools/dfII/bin: $CDS_INST_DIR/tools/dsm/bin:$PATH setenv LD_LIBRARY_PATH $CDS_INST_DIR/tools/lib:$LD_LIBRARY_PATH • Set Cadence license environment variable setenv CDS_LIC_FILE license_file • Check the special licenses! ENVISIA_SE_SI_place_route Clock_Tree_Generation Silicon_Ensemble Silicon_Ensemble_DSM

Getting started with place-and-route In the next few pages, you will become familiar with the basic commands and acronyms needed to generate a simple layout. The case study that follows lets you experiment with the software.

SE Place-and-Route Flow • Read the physical library file • Read the timing library • Read the Verilog or DEF database • Read the constraints file • Initialize the floorplan area • Place I/O cells and macros • Initialize power planning • Place standard cells • Generate the clock tree • Route special nets (power, clock) • Generate and optimize routing • Verify timing goals have been met • Write out files for backannotation

Login into the workstation Login: cadence Password: cadence Guest user with full rights

Start up Silicon Ensemble Middle click at an empty place of the screen and the Engineering Tools popup window opens. Make a left click on the OPUS Silicon Ensemble This solution is site specific!

Start up Silicon Ensemble The Silicon Ensemble graphical user interface opens. main design window object selection window message window command line

Library files Physical Library File (LEF) A Library Exchange Format (LEF) file is an ASCII file that contains library information for a class of designs: •Library data in ASCII format •Wire unit parasitic information •Detailed cell size and pin location •Routing level information •Macro cell definitions Timing Library File (TLF, CTLF) The TLF or CTLF file is a timing library for the standard cells. A timing library includes all of the timing information associated with a particular manufacturing process. Only a single timing library is required by the P&R flow.

Library files Physical Design Exchange Library File (DEF and PDEF) The DEF file contains physical design data such as placement and bounding box data, routing grids, power grids, pre-routes and rows. DEF can also include additional information such as routing grids, power grids, pre-routes, and rows. This physical data is an optional input that would typically be available if this were a redesign of an existing device. General Constraint Format File (GCF) General Constraints Format (GCF) is the Cadence specification for inputting System Level Constraints (SLC). GCF specifies system-level and boundary timing constraints for a design. General Constraint Format (GCF) file gives the path to the CTLF file, which is then loaded automatically.

Library files Standard Delay File (SDF) After a generic netlist is read, Standard Delay Format (SDF) data can also be loaded to include physical design constraints. In addition, timing information is conventionally stored in a SDF file. Individual net RC and design SDF timing information is annotated to the design within the synthesis software to provide an accurate timing and design rule violation view of the design.

Read the physical library Left click on the File Import LEF... Select the correct library exchange format file from the path.

Read the timing library Left click on the File Import Timing Library... Select the correct timing library file from the path.

Read the Verilog database Left click on the File Import Verilog... Read in the Verilog source files and libraries from the path.

Read the physical database Left click on the File Import DEF... Select the correct design exchange format file from the path.

Read the constraints file Left click on the File Import System Constraints… or File Import SDF… depending on the constraint type Select the correct constraints file from the path.

Save the current state Left click on the File Save As… Set the correct Design Name value Click on OK Switch on Keep Editing Current Design to leave the original design database opened. .

Initialize the floorplan area Left click on the Floorplan Initialize Floorplan... Fill out the form Switch on Abut Rows and Flip Every Other Row if physical library enables it Click on Calculate and check the result Click on OK

Place I/O cells automatically Left click on the Place IOs... Click on OK

Place I/O cells from file Left click on the Place IOs… Select I/O Constraint File On the Placement Mode tab Click on Write Click on Edit and modify the I/O order Save the file Click on OK

Fill out the I/O gaps Left click on the File Execute… Select fillperi.mac Click on OK

Place macro cells Check on the visibility and selectivity of the Cell in the Object Selection Window. Left click on Sl column Select one of the soft blocks near the lower left corner of the design Left click on the block Move the block to the corner of the core area Left click on the Move icon

Cut rows around macros Left click on the Floorplan Update Core Rows... Set Global Block Halo to the correct value Click on OK

Initialize power planning Left click on the Route Plan Power… yellow dotted line around the core shows the global topology Leave the toolbox opened!

Add power rings Left click on the Add Rings… on the Plan Power toolbox Fill out the signed fields and click on OK

Add power stripes Left click on the Add Stripes… on the Plan Power toolbox Fill out the signed fields and click on OK

Generated power plan Click on Close on the Plan Power toolbox to stop the command

Place standard cells Left click on the Place Cells… Click on Options Set Extra Sites for Clock Buffers to 0.6 (this reserves place for clock tree generator) Click OK in the Place Cells Options form Click on OK

Fill out the cell gaps Left click on the File Execute… Select fillcore.mac Click on OK

placed Save the current state Left click on the File Save As… Set the correct Design Name value Click on OK Switch on Keep Editing Current Design to leave the original design database opened. .

Route power nets Left click on the Route Connect Ring... Switch off IO Ring Click on OK

Route power nets Left click on the Route Route Power Follow Pins… Set Primary Layer Name to MET1 and Width to 2.0 Set the correct Area and Core Area values Click on OK

Generate global and detail routing Left click on the Route Wroute… Click on Options and select Optimize Wire Length Click OK in the WRoute Option form Click OK