eRM based, Full ML reuse methodology

eRM based, Full ML reuse methodology. Agenda. Why eRM. What is missing ? What in it for ME ? Closing the GAP - ML reuse principles Summary and Q & A. A glimpse into eRM. Standardization (env -> agent-> …, package structure, naming conventions) Reuse rules

eRM based, Full ML reuse methodology

E N D

Presentation Transcript

Agenda • Why eRM. • What is missing ? • What in it for ME ? • Closing the GAP - ML reuse principles • Summary and Q & A

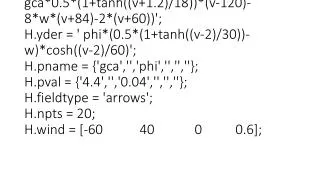

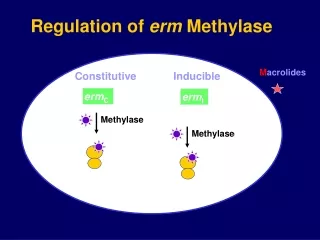

A glimpse into eRM • Standardization • (env -> agent-> …, package structure, naming conventions) • Reuse rules • Self Contained; tagged with subtype; extendable per subtype; Passiveness option • Sequences and Sequence drivers

Standard eRM usage • Usually - reusing eVCs across different environments. • use it : • in ML environment • In CL environment

What is missing ? • eRM is good for eVCs. Not sufficient for ML envs for DUTs. • eVC structure fits protocol IP. Fits Less for ML env. • ML env needs less restricted structure. • ML env needs test flow.

The Question : • How to reuse a full Module Level environment to the Chip Level environment ?

What in it for ME ? • Standardization : • All ML envs and CL env look and feel the same. • Time - CL env. is modular and can be brought up faster. • CL simulation – mainly integration bugs • Internals checkers and monitors save debug time • May catch bugs that were skipped in ML

Closing the GAP - ML reuse principles • Standardization : • Fixed basic skeleton + test flow : ML + CL envs. • Naming conventions – top ML unit, top reusable e-file, registers names • Separating reusable and non-reusable code • reset DUT / init DUT – usually not reusable. • Apply same reuse rules : • Self Contained; tagged with subtype; • extendable per subtype. Passiveness option

Example - Our SoC ARM subchip ARM eVC S S S S M M M PCM eVC OCP eVC Regs pkg vr_ad DMA PCMI Main OCP Interconnect UART RAM Regs. Bridge SDIO SDIO eVC UART eVC

Summary • Cadence needs to work on such methodologies further. (SVM ?!) • Meanwhile - Implement eRM rules for the ML env, and step from eRM forward.