Design Considerations for PXI Timing & Synchronization Systems

800 likes | 1.29k Vues

Design Considerations for PXI Timing & Synchronization Systems. Rodney Greenstreet NI Timing and Sync Technical Lead. Clock (Sampling) Basics. Physical signal. Sample clock. Sampled points. ADC. Sample Clock A. ADC. Sample Clock B. Clock Domain.

Design Considerations for PXI Timing & Synchronization Systems

E N D

Presentation Transcript

Design Considerations for PXI Timing & Synchronization Systems Rodney Greenstreet NI Timing and Sync Technical Lead

Clock (Sampling) Basics Physical signal Sample clock Sampled points

ADC Sample Clock A ADC Sample Clock B

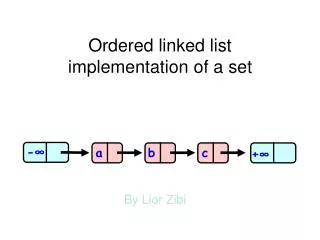

Clock Domain • A subsystem that is driven by a single clock • or by clocks that have constant phase relationships Domain 0 Domain 1

“10 MHz” Clocks Small errors at beginning of acquisition Larger errors as acquisition continues Frequency “10 MHz” Clock 1 Really 10.001 MHz 10 MHz “10 MHz” Clock 2 Really 9.999 MHz

Clock Stability is Important Frequency 10 MHz Time

Common Clock Domain Master Slave Common Clock Domain

Star Trigger Bus 10 MHz CLK Peripheral Peripheral Peripheral Peripheral PXI Timing and Triggering System Controller System Timing Slot PXI Trigger Bus 0..7 RTSI Bus 0..7 PXI_TRIG 8-line parallel trigger lines PXI_CLK10 10MHz point to point <1ns skew PXI_STAR Point to point <1ns skew

100 MHz Differential CLK SYNC100 PXI Express Hybrid Peripheral PXI Express Hybrid Peripheral PXI Express Hybrid Peripheral Differential Star Triggers PXI-1 PXI Express Star Trigger 10 MHz CLK PXI Express System Controller PXI Express System Timing Slot PXI-1 Peripheral PXI Trigger Bus (8 TTL Triggers)

Synchronization Signal Connections *There may be up to 6.5 ns of skew between PXI_Clk10 and PXIe_Clk100

Full Scale Static Engine Test Installation 8x 300 m Fiber In Control Room 395 Channels 102.4 kS/s

Flyover Test Installation 100m 427 Channels 102.4 kS/s 405 Low Cost Microphones 100m 8x 200m Fiber

Hardware Architecture Controller Controller Controller Controller Controller Controller Controller Controller Host PC GigE Switch

On-chip PXI PXI Multichassis Signal-based Synchronization Technologies Precision 10-12 sec ? 10-9 sec 10-6 sec 10-3 sec sec <10-4m 10-2m 100m 101m 102m 103m 104m 105m Global Proximity

IEEE 1588 Master Slave

On-chip PXI PXI Multichassis Signal-based IRIG-B IEEE-1588 GPS NTP TCP/IP Messages Synchronization Technologies Precision 10-12 sec Time-based 10-9 sec 10-6 sec 10-3 sec sec <10-4m 10-2m 100m 101m 102m 103m 104m 105m Global Proximity

Signal-Based … Share Physical Clocks / Triggers Time-Based Ethernet (1588) GPS Etc. Share Time Generate Signals Generate Signals

Using Time-Based Synchronization GPS Interact w/ Time 1588 FPGA-based TimeKeeper Time Reference I/O Timestamping Clock / Trig Gen IRIG DC or AM PPS

Donghai Bridge - Structural Health Monitoring with PXI • Bridge Requirements • 20-mile long, operating in harsh conditions • Long-term vibration monitoring with low-maintenance • High-level software to manage, analyze, and report on entire scale • Solution • 14 PXI systems synchronized over GPS • Continuous 24x7 operation for over 2-years Structural Health Monitoring of the Donghai Bridge with NI LabVIEW and PXI

Current Time-Based Limitations • Timekeeping traditionally digital (FPGA) implementation 212.5MHz Jitter Jitter ~100MHz Vs. 5ps RMS for Clock Sharing! Offset in ns

Disciplined Oscillator Timekeeper PXI-6682 PXI-6653 / PXIe-6674 No Dropped Edges! X Oscillator PXI_CLK10 (10MHz) DAC Time Reference Software Adjustments TimeKeeper (100MHz)

PXI TimeSync Plug-insfor RT I/O Scan Engine LVRT System Time 6682 Plug-In PXI-6682 TimeSync Framework GPS 1588 Software-Based 1588 SNTP Plug-In IRIG-B LV 2009 Timed Loop 1588

On-chip PXI PXI Multichassis Signal-based IRIG-B IEEE-1588 GPS NTP TCP/IP Messages Questions ? Precision 10-12 sec Time-based 10-9 sec 10-6 sec 10-3 sec sec <10-4m 10-2m 100m 101m 102m 103m 104m 105m Global Proximity

Contact For questions or consultation pertaining to development of applications leveraging timing and synchronization... David Nosbusch, NI Timing & Synchronization Product Manager, david.nosbusch@ni.com Todd Holthaus, NI District Manager, todd.holthaus@ni.com

Synchronization Options • Sample Clock Timed Devices • DAQ (X-series), SC Express • Oversample Clock Devices • DSA (PXIe-449x), Bridge-input SC Express • Modular Instruments • Digitizers / Scopes, FGENs

Synchronizing Data Acquisition Boards • Low frequency (< 1 MHz usually) • Clocks are slow enough to directly share between boards • Trigger propagation delay small compared to sample clock period

Synchronizing DSA Boards • Low frequency (< 1 MHz usually) • Delta-sigma ADCs require free-running oversample clock to drive conversion process • Requires reference clock or sample clock timebase synchronization (handled by NI-DAQmx) • Share high frequency oversample or 10 MHz reference clock, sync pulse, and start trigger

Synchronizing Modular Instruments • Higher frequency (up to 250 MHz) • Clocks are too fast to be directly shared between boards • Trigger propagation delay large compared to sample clock period • Requires more sophisticated architecture for synchronization (handled by NI-TClk)

Synchronize MI-Quality PXI 10MHz Clock Sys1 Edge Sys2 Edge offset using GPS Clk10 Period Share Time Aligned CLK10 Aligned CLK10 Note: This is NOT cycle-to-cycle Jitter

Modular Instruments Sync Opportunity GPS GPS TClk TClk

Extending of Time-Based TClk GPS GPS TClk TClk 1588 TClk

More Side Benefits TClk TClk Cabled Clk10 Work around TClk Limitations • > 20m • (FTE have no prop delay) • Multiple Controllers possible • Homogeneous Systems • Fewer Cables “Cabled” ps Performance • Share CLK10 Directly • Use as Timekeeper’s Timebase Triggers Cabled Clk10 MXI Time: e.g. 1588 New! Traditional TClk

Time-Based vs. Signal Based • Signal-Based • Clocks and Triggers physically connected between systems • Highest-precision synchronization • i.e. TClk, Sample Clock Synchronization • Time-Based • System components have a common reference of what time it is • Events, Triggers and Clocks can be generated based on this time • Signals can be timestamped and correlated in post-processing • Eg. Multiple Analog inputs start acquisition at 12:00 p.m. and every μs thereafter • i.e. 1588, GPS, NTP (Network Time Protocol)

Differential Star Triggers • PXIe_DSTARA, PXIe_DSTARB, PXIe_DSTARC • Differential, point-to-point connections • Matched length to within 150ps • PXIe Peripheral Slots and the System Timing Slot

Trigger Clocks • Only available on SMC devices • Devices are phase locked to a reference clock • TClk aligns the sample clocks that may not be necessarily aligned initially despite being phase locked to the 10 MHz reference clock • TClk enables extremely accurate triggering of synchronized devices

How It Plays Out • The NI-TClk driver software selects a master device • Master device credentials: • Depends on trigger (Start, Ref, Script) • TClk software calculates which device takes the longest to prep (examines number of pre-trigger samples, trigger holdoff, and other configured delay) • Device that takes longest to prep is master

Comparing PXIe_CLK100 and PXI_CLK10 • PXI_CLK10 preserves compatibility with PXI modules • PXI_CLK10 is synchronous to PXIe_CLK100 • Specifications comparison:

Using PXIe_SYNC100 • Allows a Peripheral Module to create a local version of PXI_CLK10 • Peripheral Modules can perform PXI_CLK10-synchronous communication without connecting to PXI_CLK10 • Useful for modules with PLLs or DLLs that cannot lock to a frequency as low as 10 MHz

Using PXIe_SYNC100Synchronizing Multiple Chassis • PXIe_SYNC100 can have a frequency other than 10 MHz • Modules in separate chassis can use PXIe_SYNC100 to communicate via synchronous triggers even when they are electrically farther apart than 100 ns (20.1 m) • PXIe_SYNC_CTRL controls the behavior of PXIe_SYNC100 • PXIe_SYNC_CTRL is synchronous to PXI_CLK10 • The System Timing Module provides PXIe_SYNC_CTRL

Trigger Master Slaves Trigger Clock Master Slaves Reference Clock Elements of Synchronization – Trigger & Clock • A trigger and clock to initiate and control the timing on all instruments • Clock could be sample, oversample, or reference clock • Clock could come from master or external device

Sources of Measurement Error • Skew - The degree of non-synchronism in the triggering of the various slave devices. • Drift - The accumulation of small errors in independently operating clocks • Jitter - The deviation from ideal timing of an event