HC08 ARCHITECTURE DETAILS

110 likes | 343 Vues

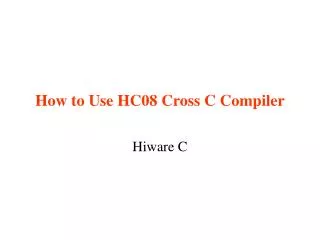

HC08 ARCHITECTURE DETAILS. MC68HC08 Architecture Details. MC68HC08 Family Nomenclature Variations Block Diagram Pins Memory Map. MC68HC08 Nomenclature. MC 68 HC 7 08 XL 36 XX B/FU 1 2 3 4 5 6 7 8 9. 1. Qualification Status: PC - no qual. XC - limited qual. MC - full qual.

HC08 ARCHITECTURE DETAILS

E N D

Presentation Transcript

MC68HC08Architecture Details • MC68HC08 Family • Nomenclature • Variations • Block Diagram • Pins • Memory Map

MC68HC08 Nomenclature MC 68 HC 7 08 XL 36 XX B/FU 1 2 3 4 5 6 7 8 9 • 1. Qualification Status: PC - no qual. XC - limited qual. MC - full qual. • 2. Historic reasons. The 68 references Motorola’s first micro-processor, the MC6800. All architectures are based of this device. • 3. Speed/Power: H - High Speed C - 5.5V L - 2.0V • 4. Memory type: Blank - ROM/ROMless 7 - EPROM/OTP 8 - EEPROM • 5. CPU type: 08 • 6. Family and Member Indicators: X - Family L- Member • 7. ROM Size: 36 KBytes ROM • 8. Temperature range: Blank - (0 to 70C) C - (-40 to 85C) M - (-40 to 125C) • 9. Package Type: B - SDIP FU - QFP

MC68HC08 Family Codes MC68HC708XL36FU A Automotive N Gen. purpose (52/56 pin) B Gen. purpose (16/20 pin) O -- avoided -- C Consumer P PC D DSP Q Future gen. purpose/cpu ext. E Gen. purpose (28/32 pin) R Future gen. purpose/cpu ext. F Telephone S Smartcard G Gen. purpose (40/42/44 pin) T Television H Future gen. purpose/cpu ext. U -- avoided -- I -- avoided -- V VFD J Future gen. purpose/cpu ext. W Future gen. purpose/cpu ext. K Fuzzy (knowledge based) X Gen. purpose (56/64/68 pin) L LCD Y Gen. purpose (80 pin) M Motor control Z Gen. purpose (100-132 pin)

MC68HC08 Member Codes MC68HC708XL36FU A Multifunction timer parts M Other (A/D, etc) B “ N “ C “ O “ D General timer parts P “ E “ Q “ F “ R “ G General timer + serial interface S Non-volatile memory + anything H “ T “ I “ U “ J “ V “ K “ W “ L “ X “ Y “ Z “

FLASH 68HC908AT32 68HC908XL36 68HC708XL36 68HC708MP16 EPROM 68HC708LN56 68HC708AS48* 68HC08XL36 68HC08MR16 68HC08AS20 ROM 68HC08LN56 68HC08AZ32 68HC08AB32 68HC08AZ24 68HC08AB24 68HC08AZ16 68HC08AB16 68HC08AB0 68HC08AZ0 *-Prototyping General Gen. Purp. Consum. CAN J1850 M o t o r Qty. Only Purpose Auto./Ind. Comm. Auto./Ind. Auto./Ind. C o n t r o l New 68HC08 Introductions

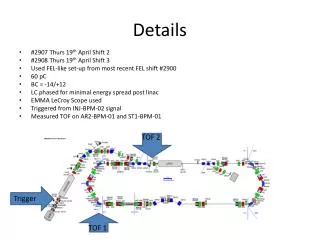

V DDA MC68HC708XL36Block Diagram INTERNAL BUS M68HC08 CPU PTA7 – PTA0 CPU ARITHMETIC/LOGIC REGISTERS UNIT (ALU) DIRECT MEMORY ACCESS MODULE PTB7 – PTB0 CONTROL AND STATUS REGISTERS — 88 BYTES BREAK MODULE USER EPROM — 36,864 BYTES PTC7 – PTC0 LOW-VOLTAGE INHIBIT MODULE USER RAM — 1024 BYTES PTD7/KBD7 – PTD0/KBD0 COMPUTER OPERATING PROPERLY MODULE MONITOR ROM — 240 BYTES PTE7/TCH3 PTE6/TCH2 USER EPROM VECTOR SPACE — 32 BYTES TIMER INTERFACE PTE5/TCH1 MODULE PTE4/TCH0 OSC1 PTE3/TCLK CLOCK GENERATOR OSC2 PTE2/TxD MODULE SERIAL COMMUNICATIONS INTERFACE CGMXFC PTE1/RxD MODULE PTE0 PTF5 SYSTEM INTEGRATION RST PTF4 MODULE PTF3/MISO PTF2/MOSI SERIAL PERIPHERAL INTERFACE IRQ1 /V MODULE IRQ PTF1/SPSCK PP MODULE IRQ2 PTF0/ SS POWER-ON RESET PTG3 – PTG0 MODULE (64-PIN PACKAGE ONLY) V SS V DD POWER PTH3 – PTH0 (64-PIN PACKAGE ONLY) CGND/EVss

Overview of Pin Functions • BASIC SUPPORT PINS • VDD , VSS Power (+5V) and Ground • OSC1, OSC2 Crystal connection for on chip oscillator • RST External Reset, bidirectional • IRQ1/VPP, IRQ2 External Interrupt Request IRQ1 is also the EPROM programming power pin • CGND\EVSS Clock Ground • VDDA Clock Generation Module Power Supply • CGMXFC External Filter Capacitor for Clock Generation Module

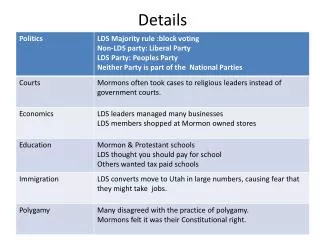

$0000 $000F $0010 $0012 $0013 $0019 $001A $001B $001C $001E $0020 TIM $0031 Registers $0032 DMA Registers $004E $FFE0 $FFFF MC68HC708XL36MEMORY MAP $0000 – $004F I/O Registers (80 Bytes) Port A - H Registers RAM (1024) Bytes $0050 – $044F SPI Unused (27,056 Bytes) $0450 – $6DFF Registers EPROM (36,864 Bytes $6E00 – $FDFF SCI Registers SIM Break Status Register $FE00 SIM Reset Status Register $FE01 XIRQ Registers Reserved (1 Byte) $FE02 SIM Break Flag Control Reg. $FE03 CGM Reserved/Unimplemented $FE04 – $FE06 Registers $FFE0 - FFE1 IRQ2 EPROM Control Reg. $FE07 Reserved (4 Bytes) $FE08 – $FE0B $FFE2 - FFE7 SCI Mask Option Reg $001F Break Addres Reg. High $FE0C $FFE8 - FFEB SPI Break Address Reg. Low $FE0D Break Status/Control Reg. $FE0E $FFEC - FFF5 TIM LVI Status/Control Reg. $FE0F Monitor ROM (240 Bytes) $FFF6 - FFF7 DMA $FE10 – $FEFF $FFF8 - FFF9 PLL Unused (192 Bytes) $FF00 – $FFBF $FFFA - FFFB IRQ1 Reserved (32 Bytes) $FFC0 – $FFDF $FFFC - FFFD SWI Vectors (32 Bytes) $004F Unused $FFFE - FFFF Reset COP Control Reg.