Essential Concepts in Code Generation: Compiler Phases and Techniques

This document provides an in-depth overview of fundamental issues and techniques in code generation within compiler design. Key topics include code selection, register allocation, instruction ordering, and simplifications that enhance efficiency. It discusses practical approaches such as generating code for expressions using both stack and register machines. The concept of partial evaluation and its role in generating equivalent programs is also explored, illustrated by examples. Additionally, the document outlines simple code generation for various machine models, emphasizing local decisions and fixed translations for nodes.

Essential Concepts in Code Generation: Compiler Phases and Techniques

E N D

Presentation Transcript

Code Generation Mooly Sagiv html://www.cs.tau.ac.il/~msagiv/courses/wcc03.html Chapter 4.2

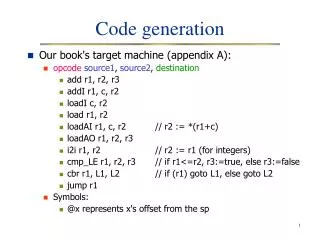

Code generation issues • Code selection • Register allocation • Instruction ordering

Simplifications • Consider small parts of AST at time • One expression at the time • Target machine simplifications • Ignore certain instructions • Use simplifying conventions

Outline • Partial evaluation in the nutshell • Simple code generation for expressions (4.2.4) • Pure stack machine • Pure register machine • Code generation of basic blocks (4.2.5) • Automatic generation of code generators (4.2.6) • Register Allocation by Graph Coloring (4.2.7) Next week

Partial Evaluator Program’ Program Input 1 Input 2 Partial Evaluation • Partially interpret static parts in a program • Generates an equivalent program

Example int pow4(int n) { return n * n * n *n; } int pow(int n, int e) { if (e==0) return 1; else return n * pow(n, e-1); } e=4

Example2 Bool match(string, regexp) { switch(regexp) { …. } } regexp=a b*

Partial Evaluation Generalizes Compilation Partial Evaluator Program Interpreter AST Program Input

Simple Code Generation • Fixed translation for each node type • Translates one expression at the time • Local decisions only • Works well for simple machine model • Stack machines (PDP 11, VAX) • Register machines (IBM 360/370) • Can be applied to modern machines

Simple Stack Machine SP Stack BP

Example Push_Local #p Push_Const 5 Add_Top2 Store_Local #p p := p + 5

Simple Stack Machine Push_Local #p Push_Const 5 Add_Top2 Store_Local #p SP BP+5 7 BP

Simple Stack Machine Push_Local #p Push_Const 5 Add_Top2 Store_Local #p SP 7 BP+5 7 BP

Simple Stack Machine SP 5 Push_Local #p Push_Const 5 Add_Top2 Store_Local #p 7 BP+5 7 BP

Simple Stack Machine Push_Local #p Push_Const 5 Add_Top2 Store_Local #p SP 12 BP+5 7 BP

Simple Stack Machine Push_Local #p Push_Const 5 Add_Top2 Store_Local #p SP BP+5 12 BP

Register Machine • Fixed set of registers • Load and store from/to memory • Arithmetic operations on register only

Example Load_Mem p, R1 Load_Const 5, R2 Add_Reg R2, R1 Store_Reg R1, P p := p + 5

Simple Register Machine Load_Mem p, R1 Load_Const 5, R2 Add_Reg R2, R1 Store_Reg R1, P R1 R2 x770 7 memory

Simple Register Machine 7 Load_Mem p, R1 Load_Const 5, R2 Add_Reg R2, R1 Store_Reg R1, P R1 R2 x770 7 memory

Simple Register Machine 7 5 Load_Mem p, R1 Load_Const 5, R2 Add_Reg R2, R1 Store_Reg R1, P R1 R2 x770 7 memory

Simple Register Machine 12 5 Load_Mem p, R1 Load_Const 5, R2 Add_Reg R2, R1 Store_Reg R1, P R1 R2 x770 7 memory

Simple Register Machine 12 5 Load_Mem p, R1 Load_Const 5, R2 Add_Reg R2, R1 Store_Reg R1, P R1 R2 x770 12 memory

Simple Code Generation for Stack Machine • Tree rewritings • Bottom up AST traversal

Example Subt_Top2 - Mult_Top2 Mult_Top2 * * Mult_Top2 Push_Constant 4 Push_Local #b Push_Local #b b b 4 * a c Push_Local #c Push_Local #a