Scalable Test Pattern Generator Design Method for BIST

This paper discusses a method for BIST design with a big trade-off between fault coverage, test time, area overhead, and design time. It introduces a Column-Matching algorithm for decoder design in Mixed-Mode BIST, achieving better results compared to existing methods.

Scalable Test Pattern Generator Design Method for BIST

E N D

Presentation Transcript

Scalable Test Pattern Generator Design Method for BIST Petr Fišer, Hana Kubátová Czech Technical University in PragueFaculty of Electrical EngineeringDept. of Computer Science & Engineering

Outline • Motivation • Proposed BIST scheme • The Column-Matching algorithm • Customizing the design process • Experimental results • Conclusions LATW 2008, 17. – 20.2., Puebla

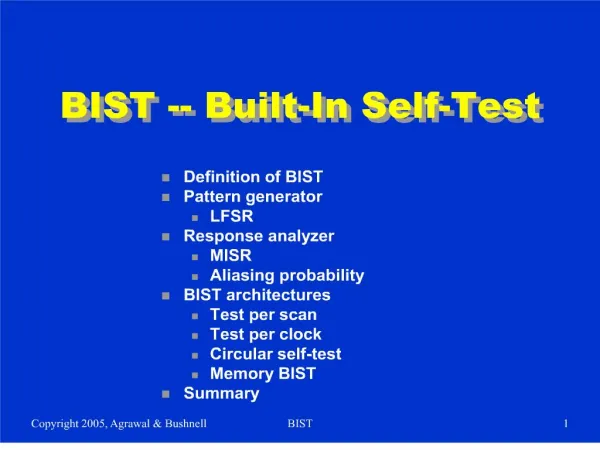

Motivation Four important aspects in BIST: • Fault coverage • Test time • BIST area overhead • BIST design time LATW 2008, 17. – 20.2., Puebla

Motivation Different ASIC designers have different requirements for BIST • Design the BIST equipment as fast as possible, regardless the area overhead and the fault coverage (no time to wait, the deadline is approaching!) • Design the BIST equipment to be as small as possible, regardless the time it takes (low power) • High fault coverage is the most important aspect, the area overhead is next. The design time is not that important (common practice) LATW 2008, 17. – 20.2., Puebla

Motivation We propose a method offering a bigtrade-off between all these criteria: • Fault coverage • Test time • BIST area overhead • BIST design time LATW 2008, 17. – 20.2., Puebla

Motivation We propose a method offering a bigtrade-off between all these criteria: • Fault coverage • Test time • BIST area overhead • BIST design time Given by ATPG100% fault coverage will be considered LATW 2008, 17. – 20.2., Puebla

The Proposed BIST • Mixed-Mode (Hybrid) BIST • Two separated phases: pseudorandom and deterministic LATW 2008, 17. – 20.2., Puebla

The Decoder Design The Column-Matching method Deterministic BIST: • LFSR produces pseudo-random code words(C-matrix) • These are then transformed into deterministic tests computed by ATPG(T-matrix) LATW 2008, 17. – 20.2., Puebla

The Decoder Design The Column-Matching method – basic principles • Try to reorder test patterns, so that most of the Decoder outputs will be implemented as wires – a Match • This will be accomplished when two particular columns of the LFSR and test matrices will be equal • Combinational logic – the order is insignificant • Unmatched outputs have to by synthesized by a Boolean minimizer LATW 2008, 17. – 20.2., Puebla

The Decoder Design The Column-Matching method – example y0 = x0 y1 = x1 y2 = x2’ y3 = x1 y4 = x0’ + x1 LATW 2008, 17. – 20.2., Puebla

Mixed-Mode BIST • Simulate severalLFSR patterns • Determine undetected faults • Compute a test for them (ATPG) • Design a decoder generating vectors for this test and following LFSR patterns LATW 2008, 17. – 20.2., Puebla

Mixed-Mode BIST ColumnMatching LATW 2008, 17. – 20.2., Puebla

Mixed-Mode BIST Decoder Switch LATW 2008, 17. – 20.2., Puebla

Scaling the Lengths of the Phases Pseudorandom phase • To detect easily detectable faults Deterministic phase • To generate deterministic vectors LATW 2008, 17. – 20.2., Puebla

Reducing the LFSR Width By weighted pattern testing • 3-weight logic • The weights are computed for RPRFs • The LFSR inputs are AND-ed and OR-ed to produce weights LATW 2008, 17. – 20.2., Puebla

Reducing the LFSR Width ISCAS’89 s13207.1 benchmark (700 inputs) LATW 2008, 17. – 20.2., Puebla

Experimental Results – Area Overhead Comparison Comparison with state-of-the-art methods. Equal test lengths, the area overhead is compared • Compared with: • Bit-Fixing[N.A. Touba, E.J. McCluskey: Bit-Fixing in Pseudorandom Sequences for Scan BIST, IEEE Transactions on CAD, Vol. 20, No. 4, April 2001, pp. 545-555] • Weighted-pattern BIST[S. Wang: Low Hardware Overhead Scan Based 3-Weight Weighted Random BIST. Proc. 2001 IEEE International Test Conference] • Row Matching[M. Chatterjee, D.K. Pradhan: A BIST Pattern Generator Design for Near-Perfect Fault Coverage, IEEE Transactions on Computers, vol. 52, no. 12, December 2003, pp. 1543-1558] CM always better CM better in 71% CM better in 60% LATW 2008, 17. – 20.2., Puebla

Experimental Results Hard-to-test (and “big”) benchmarks LATW 2008, 17. – 20.2., Puebla

Conclusions • The Column-Matching principle proposed • Influence of the lengths of the phases is studied • Very scalable, many design parameters freely adjustable • The results obtained by CM are mostly better (wrt. the area overhead) than those obtained by state-of-the-art methods • The method should serve as a basic guideline how to design more complex BIST designs, i.e., the multiple‑scan chain based BIST, the STUMPS architecture, etc. • It can be very advantageously used to test SoCs, since the LFSR may be reused for more cores. LATW 2008, 17. – 20.2., Puebla