Serial Data Link on Advanced TCA Back Plane

Serial Data Link on Advanced TCA Back Plane. M. Nomachi and S. Ajimura Osaka University, Japan. CAMAC – FASTBUS – VME / Compact PCI What ’ s next?. Downsizing ( Rack-Crate-Module-Chip- ). CPU. CAMAC crate. BUS. module. module. module. Downsizing ( Rack-Crate-Module-Chip- ). Module.

Serial Data Link on Advanced TCA Back Plane

E N D

Presentation Transcript

Serial Data Link onAdvanced TCA Back Plane M. Nomachi and S. Ajimura Osaka University, Japan CAMAC – FASTBUS– VME / Compact PCI What’s next?

Downsizing (Rack-Crate-Module-Chip-) CPU CAMAC crate BUS module module module RT2005 Nomachi, M.

Downsizing (Rack-Crate-Module-Chip-) Module CPU Network Interface Is CPU at right place? Should we have parallel BUS on board? Do we still need crate? BUS FPGA FPGA FPGA Questions RT2005 Nomachi, M.

Functionality of a CPU • Data readout • Register/memory access • Block transfer • Data processing • Application dependent • Network protocol • TCP/IP etc. • It is indispensable function for network DAQ. CPU sits at the boundary between memory mapped I/O and network RT2005 Nomachi, M.

DAQ architecture Network Network Network Rack Crate CPU Memory Mapped I/O CPU Module Memory Mapped I/O CPU Chip RT2005 Nomachi, M.

DAQ architecture Network Rack We choose memory mapped I/O in a crate. It makes easy to maintain CPU. There were many bad experiences on embedded CPUs. Crate CPU Memory Mapped I/O Module Chip RT2005 Nomachi, M.

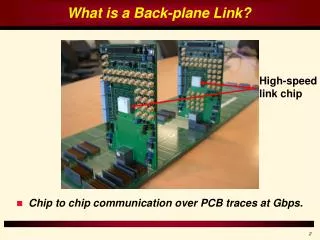

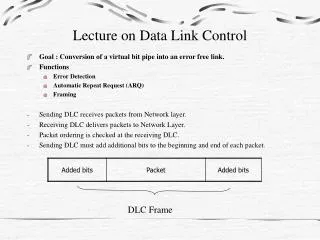

Downsizing the interconnections • Parallel bus on board • Occupy large area • Need many pins • Serial data link will be a solution • It can be low noise/low power • Less number of drivers • It may have longer latency • 1 ns – 100 ns. • Memory mapped I/O over serial data link. RT2005 Nomachi, M.

SpaceWire • Remote Memory Access Protocol (RMAP) • SpaceWire was presented by S. Parkes. • RMAP is a protocol on the SpaceWire standard. • Register access has large overhead. • Block transfer works almost full speed. • It meets the requirements. Good enough. • PCI express and the other protocol may also meet the requirements. However, they may use too much logic (x10) for front-end FPGAs. RT2005 Nomachi, M.

Do we need crate? • Serial data link is very flexible. • System with no crate is possible. • Functionality of crates: • Mechanical Housing / Shielding • Power supply • Cooling • We need a crate. • VME • 6U is too small • Power is a problem on VME. -5.2V etc. RT2005 Nomachi, M.

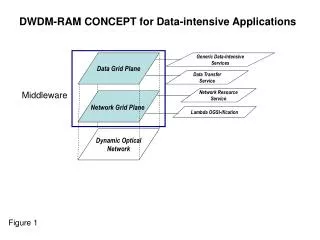

Advanced TCA • Features (ATCA was presented by B. Martin and S. Dhawan) • -48V DC power supply and on board DC converter for any voltages required. • 8U x 280 mm • Dual Star point to point differential connection • No definite protocol. • VME back plane is for VME protocol. While, ATCA back plane is only defined as 100 ohm differential. Any protocol can use ATCA back plane. ( for example, ATCA for physics instrumentation) RT2005 Nomachi, M.

DAQ system Trigger module Front-end module Front-end Global trigger Trigger logic Pipe-line buffer Trigger control readout buffer Read out module Readout control Second level trigger network CPU To event builder RT2005 Nomachi, M.

Dual star connection Trigger module Read out module CPU (T-kernel) • Asynchronous signals • (4 links) • Trigger/Reset • Local trigger/Busy SpaceWire link (4 links) Front-end module Front-end module Front-end module Front-end module Front-end module RT2005 Nomachi, M.

There are 4 ports for one channel. • One port has one output and one input. • In order to make signal extraction easy, • 2 ports are used. (SpW uses 2 ports) • The other 2 ports are to extend band width. • It makes possible to use 4-layers PCBs. RT2005 Nomachi, M.

Trigger module 16 LVDS in 16 LVDS out 8 NIM in 8 NIM out Power consumption is about 10W Cyclone EP1C12 for trigger logic Cyclone EP1C6 for SpW 100Mbps SpW RT2005 Nomachi, M.

500 MHz FADC 8 ch analog input FADC mezzanine card is developed at KEK (FINESSE format) Power consumption is About 20W Cyclone EP1C6 (cheaper than 40 Euro) Cyclone EP1C12 for router 100Mbps SpW (8~9 MB/s from the module) Readout buffer with 128Mb SDRAM waiting second level trigger RT2005 Nomachi, M.

ATCA crate One crate holds 96ch of 500MHz FADCs. Total power is expected to be 260 W. RT2005 Nomachi, M.

Summary • SpaceWire Remote Memory Access Protocol provides compact and flexible interconnection in a module and inter-module connection. • Advanced TCA provide dual star LVDS connections. They are good to be applied for DAQ system • Downsizing may continue. • We might have another solution in the future. RT2005 Nomachi, M.