Chapter5: Synchronous Sequential Logic – Part 2

Chapter5: Synchronous Sequential Logic – Part 2. Originally by Reham S. Al- Majed. Outline. Analysis of clocked SC Analysis with D FF. Analysis with JK FF. Analysis with T FF. Mealy and Moore Models of FSMs. SC Analysis.

Chapter5: Synchronous Sequential Logic – Part 2

E N D

Presentation Transcript

Chapter5: Synchronous Sequential Logic– Part 2 Originally by Reham S. Al-Majed Imam Muhammad Bin Saud University

Outline • Analysis of clocked SC • Analysis with D FF. • Analysis with JK FF. • Analysis with T FF. • Mealy and Moore Models of FSMs.

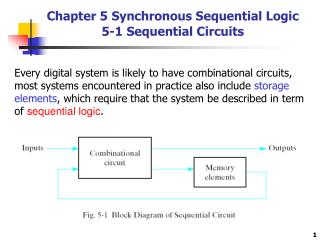

SC Analysis • Analysis describes what a given circuit will do under certain conditions. • How changes in input with the current state will affect next state and output. • Given: logic diagram of a SC consists of FF and gates. • Goal: • Find State Equations ( transition equations). • They describe the behavior of SC algebraically. • They specify the next state as a function of the present state and inputs. • Find State Table. need state equations. • Find State Diagram. need state table.

SC Analysis • To achieve any of the previous goals of SC Analysis we need to find: • Input equations( also called excitation equations): Boolean functions that describe the part of the circuit that generate inputs to FF algebraically. • Output equations: Boolean functions that describe algebraically the part of the CC that generate external output. • Characteristic equations of the used FF: • The characteristic equation for the D FF: Q(t+1) = D • The characteristic equation for the JK FF: Q(t+1)= JQ’+K’Q • The characteristic equation for the T FF: Q(t+1)= TQ • Input and output equations provide the necessary information to draw the logic diagram of SC.

Example • Find the input and output equations of the following SC logic diagram. • FFs input equations: DA= Ax + Bx DB= A’x • Output equation: y=(A+B)x’

SC Analysis • To achieve the first goal ( finding state equations): • Determine input equations. • Substitute the input equations into FF characteristic equations to obtain the next state of all FFs. • Write down the output equations.

Example Analysis with D FF • Analyze the logic diagram by finding the state equations: • FFs input equations: DA= Ax + Bx DB= A’x • The characteristic equation for D FF :Q(t+1) = D • Substitute to find state equations: A(t+1) = DA A(t+1) = Ax + Bx B(t+1)= DB B(t+1) = A’x • Output equation: y=(A+B)x’

SC Analysis • To achieve the second goal ( finding state table) • After finding the state equations and output equations. • Draw a table that: • Consists of four sections: present state, input, next state, and output. • Has all possible binary combination of present states (#m) and inputs(#n) the table has 2m+n rows. • Fill the next state and output sections of the table according to • The state equations you obtained in step 1. OR • The binary values of inputs to FFs along with characteristic table of a FF.

Example Analysis with D FF • Analyze the logic diagram by finding the state table: • From previous slide: • State equations: A(t+1) = Ax + Bx B(t+1) = A’x • Output equation: y=(A+B)x’

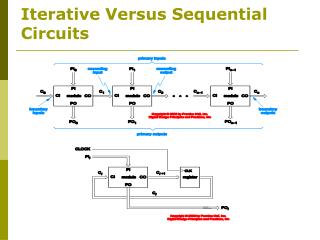

SC Analysis • To achieve the third goal ( finding state diagram): • Draw circles that represent states of the FFs • The number of circles you need depend on the number of the FFs the circuit has if the SC has n FFs, then you need 2n circles/states. • Each circle is labeled with a binary number that identifies the state of FFs. • Draw directed lines the connect circles according to the state table • The source is the present state. • The destination is the next state. • Label each line with two binary numbers separated by a slash. • The first number is the input value during the present state. • The second number is the output. input/output AB AB

Example Analysis with D FF • Analyze the logic diagram by finding the state diagram: 1/0 0/0 0/1 00 10 0/1 1/0 0/1 1/0 01 11 1/0

Example Analysis with JK FF • Find state equations of the following SC logic diagram. • FFs input equations: JA= B KA= Bx’ JB= x’ KB= A • The characteristic equation for D FF :Q(t+1)= JQ’+K’Q • Substitute to find state equations: A(t+1) = JAA’ +K’A A A(t+1) = BA’ + (Bx’)’A = A’B+AB’+Ax B(t+1) = JBB’ +K’B B B(t+1) = x’B’ + (A)’ = B’x’ + ABx+ A’Bx’ • Output equation: There is no external output.

Example Analysis with JK FF • Find state table of the previous SC logic diagram. • Fill Next state A, B from State equations: A(t+1) = A’B+AB’+Ax B(t+1) = B’x’ + ABx+ A’Bx’ OR • Use characteristics table of FF FFs input equations: JA= B KA= Bx’ JB= x’ KB= A

Example Analysis with JK FF • Find state table of the previous SC logic diagram. • Fill Next state A, B from State equations: A(t+1) = A’B+AB’+Ax B(t+1) = B’x’ + ABx+ A’Bx’ OR • Use characteristics table of FF FFs input equations: JA= B KA= Bx’ JB= x’ KB= A

Example Analysis with JK FF • Find state diagram of the previous SC logic diagram.

Exercise 1 • Find the state equations, state table, and state diagram of the following SC logic diagram.( page 219) y

Exercise 2 • Find the state equations, state table, and state diagram of the following SC logic diagram. (page 214)

Mealy and Moore Models of FSM • The most general model of SC has inputs, outputs, and internal states. • However, there are two different models of SC: • The Mealy model: • The output is a function of both the present state and the input. • The Moore model: • The output is a function of onlythe present state.

Mealy and Moore Models of FSM • In Mealy model: • The outputs may change if the inputs change during the clock cycle outputs may have false values. • Synchronize the inputs with a clock. • In Moore model: • The outputs are synchronized with the clock since they depend on FF outputs only.