Cutting-Edge Monolithic Active Pixel Sensors: Tracking Performances and Radiation Tolerance

110 likes | 212 Vues

Discover the latest advancements in CMOS sensors, their operation, resolution, radiation tolerance, and applications in particle detection. Get insights on prototype developments, design improvements, and performance evaluations in various testing environments and technologies. Dive into the detailed analysis of noise levels, charge loss, and efficiency metrics from neutron radiation tests to beam exposure experiments. Explore the future potential of CMOS MAPS for enhanced detection and signal processing capabilities.

Cutting-Edge Monolithic Active Pixel Sensors: Tracking Performances and Radiation Tolerance

E N D

Presentation Transcript

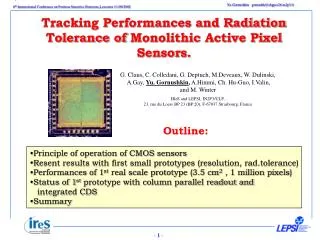

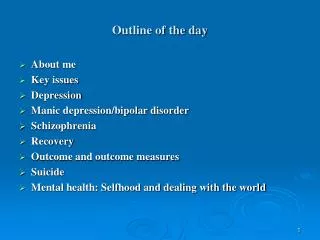

Tracking Performances and Radiation Tolerance of Monolithic Active Pixel Sensors. • G. Claus, C. Colledani, G. Deptuch, M.Deveaux, W. Dulinski, A.Gay, Yu. Gornushkin, A.Himmi, Ch. Hu-Guo, I.Valin,and M. Winter • IReS and LEPSI, IN2P3/ULP, 23, rue du Loess BP 23 (BP 20), F-67037 Strasbourg, France Outline: • Principle of operation of CMOS sensors • Resent results with first small prototypes (resolution, rad.tolerance) • Performances of 1st real scale prototype (3.5 cm2 , 1 million pixels) • Status of 1st prototype with column parallel readout and • integrated CDS • Summary

Idea and principle of operation • CMOS MAPS are replacing CCDs in visible light applications (still and video cameras, web-cameras, cell phones) – low power consumption, cheap! • To use them also for m.i.p. detection In Strasbourg (IReS-LEPSI) since 1999 • Twin-tub (double well) CMOS process with moderately doped epitaxial layer providing long minority carrier lifetime • Charge is generated in epitaxial layer (low doping): Q~80e--h/mm • Charge is collected through thermal diffusion by n-well/p-epi diode • No depletion potential applied • Potential barriers at layer interfaces confine the charge – improving collection efficiency • Charge-Voltage conversion on pixel • The device can be fabricated using a standard CMOS process, • P-type low resistivity Si g only NMOS transistors allowed

First Prototypes - Summary of Performances MIMOSA I die size 3.6 × 4.2 mm2 Examples of pixel layouts M I: 20× 20 µm2 Device internal architecture e.g. MIMOSA II High performances in m.i.p. detection established: S/N~30, e>99%, ssp~1.5-2 mm

Recent MIMOSA-1 results The spatial resolution as a function of ADC-bit encoding ( real signals “digitized” offline): even with 3-4 bits s ~2-3 mm Real particle clusters overlapped and combined distribution approximated by charge distribution function fot 2 hits. Hits are well separated at distances > 30 mm.

MIMOSA-4 test results: 0.35 mm AMS process without epitaxial layer but with low doping (resistivity) substrate • p-substrate process (~1015cm-3) • 4 arrays 64x64 pixels - pixel pitch 20x20 mm2 • diode (nwell/p-epi) size 2x2 mm2 - 1.8 fF • serial analogue readout - max. clock freq.: 20 MHz • die size 3.7x3.8 mm2 • technology 3M+2P • power supply 3.3 V • radiation tolerant transistor design • new structures of charge sensing elements: - charge spill-gate, - current mode pixel, - self-biasing diodes • Observed performances with 120 GeV/c p- at CERN-SPS: • Detection efficiency ~99.7% • S/N ~30 but charge spread is wider • Spatial resolution ~4 mm (20 mm pitch) Technology without epitaxial layer seems worth investigating and optimizing

Neutron radiation tolerance Chips irradiated with neutron sources at JINR and CEA-Saclay reactors were tested with Fe55 X-ray source. Noise as a function of fluence: Observed charge loss as a function of fluence: Charge loss is observed only for fluences >1011 n/cm2 what is 2 orders of magnitude more than it is expected for TESLA!

MIMOSA 5: big chip - simple quick start solution 19.4 mm One chip ~106 pixels of 17x17 mm2 • AMS 0.6 µm process with ~14 µm epitaxial layer • analogue readout - with hardware processing (CDS, pedestal subtraction, S/N analysis, sparsification on-line) • stitching: coarse - 100 µm + scribeline, option:precise – 1 mm • Lot of 6”wafers 44 kEuro 17.35 mm

MIMOSA-5 tests The chip (4 matrices of 512512 pixels (17x17 mm2 ) etched down to 120 mm was exposed to 120 GeV/c p- beam at CERN-SPS The same process as MIMOSA-1 the same performances expected? Noise larger than in case of MIMOSA-1 (different serial r.o.architecture – double source follower stage) Epitaxy layer ~14 mm charge ~1000e- Preliminary results: Noise mean ENC 20.7 e- Seed pixel S/N 23 Detection efficiency e~99.3%, ssp~1.7mm, sgain 2-3% close to those of MIMOSA-1

MIMOSA-5 response to inclined tracks(very preliminary): Total charge follows cos-1(q) S/N grows as well (saturation observed due to geometrical effect at large angles) MIMOSA-5 tests will continue in October 2002 at CERN-PS

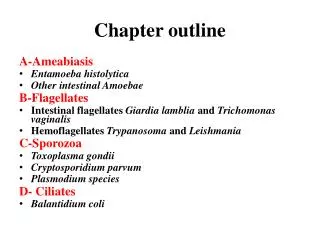

MIMOSA-6 – first sensor with integrated signal processing • 0.35 MIETEC technology (same as MIMOSA-2) • IReS-LEPSI/DAPNIA collaboration • 24 column readout in parallel • 128 pixels per column • 5MHz effective readout frequency (30MHz clock, 6 clock cycles/pixel) • Amplification (x5.5),Correlated Double Sampling on pixel • Discriminators integrated on chip periphery (1 per column) • Power dissipation ~500 mW per column Chip layout: Pixel layout: 28x28 mm2 Matrix of 128x30 pixels AC coupling capacitor 29 transitstors Discriminators Chips are expected back from foundry this days. Test results - by the end of 2002. Charge storage capacitors

Summary: • The good performance of CMOS MAPS in charge particle detection has been succesfully established with 4 generations of small scale prototypes: • e99%, ssp~1.5-2.5 mm, S/N~30, s2hit~30 mm • Tolerance to neutrons exceeds TESLA requirements by more than 2 orders of magnitude! • Preliminary results from MIMOSA-5 tests indicate that these performances are reproducible with real size detectors • (~3.5 cm2, 120 mm thin) • First chip with integrated signal processing functions (CDS+A+D) is coming back from fabrication soon tests in October 2002 • R&D programme on CMOS MAPS TESLA Vertex Detector in a collaboration of 10 labs in F-UK-CH-NL-D+… is under way.