Multi-operand Addition

160 likes | 236 Vues

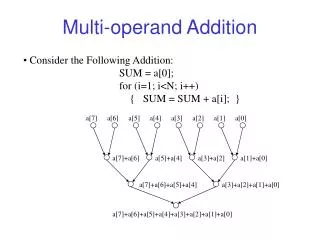

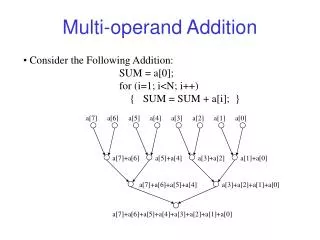

Multi-operand Addition. Consider the Following Addition: SUM = a[0]; for (i=1; i<N; i++) { SUM = SUM + a[i]; }. a[7]. a[6]. a[5]. a[4]. a[3]. a[2]. a[1]. a[0]. a[7]+a[6]. a[5]+a[4]. a[3]+a[2]. a[1]+a[0]. a[7]+a[6]+a[5]+a[4]. a[3]+a[2]+a[1]+a[0].

Multi-operand Addition

E N D

Presentation Transcript

Multi-operand Addition • Consider the Following Addition: SUM = a[0]; for (i=1; i<N; i++) { SUM = SUM + a[i]; } a[7] a[6] a[5] a[4] a[3] a[2] a[1] a[0] a[7]+a[6] a[5]+a[4] a[3]+a[2] a[1]+a[0] a[7]+a[6]+a[5]+a[4] a[3]+a[2]+a[1]+a[0] a[7]+a[6]+a[5]+a[4]+a[3]+a[2]+a[1]+a[0]

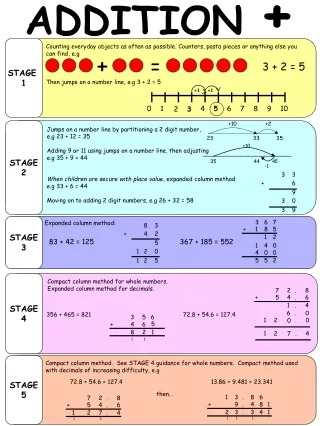

Multi-operand Addition a[7] a[6] a[5] a[4] a[3] a[2] a[1] a[0] a[7]+a[6] a[5]+a[4] a[3]+a[2] a[1]+a[0] a[7]+a[6]+a[5]+a[4] a[3]+a[2]+a[1]+a[0] a[7]+a[6]+a[5]+a[4]+a[3]+a[2]+a[1]+a[0] • O(lg2N) – Lower Bound – Theoretical Lower Limit • This is “Binary Reduction” Operation • Theoretical Time to Add Two Values • O(n) – Carry Ripple Operation • O(lg2n) – CLG/CLA tree/Prefix/Carry Skip/Carry Select • O(1) – Avizienis/Takagi Signed Digit Arithmetic

Multiplication • Multiplication Requires Multi-operand Addition • Dot Product Requires Multi-operand Addition • Defer Carry Assimilation • Represent Intermediate Sums Redundantly

Carry Save Adders • FA Used in This Configuration is Also Known as a 3:2 Compressor

Dot Notation 3:2 Compressor 2:2 Compressor