Number and Arithmetic Circuits

Number and Arithmetic Circuits

E N D

Presentation Transcript

1. Number and Arithmetic Circuits (Review)

2. Learning Objectives How are numbers represented in digital circuits?

How are numbers are added, subtracted?

3. Unsigned Integers Decimal integer: base-10 or radix-10

Binary integer: base-2 or radix-2

LSB, MSB, nibble, byte

4. Unsigned Integers Octal and Hex integers

Any radix r,

Radix-8: octal

Radix-16: Hex

Conversion between decimal, binary, octal and hex

(857)10=(1101011001)2

(101 011 010 111)2=(5327)8

(1010 1111 0010 0101)2=(AF25)16

7. Signed Numbers

8. Signed Numbers Sign-and-magnitude

Magnitude of both positive and negative in the same way

Sign bit 0 ? positive; sign bit 1 ? negative

Example: +5=0101, -5=1101

1�s complement

-p:

By complementing each bit of the number

2�s complement

-p:

By complementing each it and adding 1

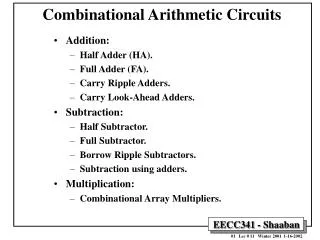

10. Half-adder

11. Full-adder

12. Ripple-Carry Adder

13. 2�s Complement Addition

14. 2�s Complement Subtraction

15. Adder/subtractor unit

16. Number and Arithmetic Circuits (Verilog)

17. Full adder -- primitives

18. Full adder -- assign

19. 4-bit adder--instantiation

20. Verilog fundamental Lexical conventions

4-value logic

Data types: nets and registers

Port connection rules

21. Lexical Conventions White space characters are ignored:

SPACE, TAB, new line, blank lines

Two forms to introduce comments

single line: begin with //

multiple lines: /*�..long comments */

Verilog is case sensitive

Lower case letters are unique from upper case letter

All Verilog keywords are lower case

Identifiers

begin with an alphabetic character or the underscore character

may contain alphabetic characters, numeric characters, _, and $

up to 1024 characters long.

The instance of a module must be named while the instance name of a primitive is optional.

`include � *.v�

22. Examples of lexical conventions

23. Set of Logic Values Sometimes, {0, 1} is not enough

24. Logic Values in Verilog 0: Logical 0

1: Logical 1

X: unknown

Z: high impedance, floating state

25. X and Z a = b = 0: c = Z

a = b = 1: c = X

Initially, every line is X

X is used in simulation. In real circuit, the value is determined by the circuit

26. Representation of numbers

27. Data types

28. Nets Note that net is not a keyword but represents a class of data types.

Default type of net is wire.

A net is assigned value, by

A primitive

Module

Continuous assignment

29. Nets wire (default)

tri

wand

wor

triand

trior

30. Net Declaration wire[7:0] data_bus; // 8-bit vector wire, data_bus[7] -> MSB

wire[0:3] control_bus; // control_bus[0] -> MSB

data_bus[5], data_bus[3:5], data_bus[k+2] // access

wire scalared[7:0] bus_a; // �scalared� is default

wire vectored[7:0] bus_b; // Individual bits may not be referenced

wire y1, z_5; // Multiple declaration

wire A = B+C, D = E+F; // Implicit continuous assignment

31. Register Data Types reg � stores a logic value

integer � support computation

time � stores time as a 64-bit unsigned quantity

real � stores values as real numbers

realtime � store time values as real numbers

32. Examples of register data types reg

reg A_Bit_Register;

reg [31:0] A_word;

integer (used for counting, index in loops)

Integer K; �

For (K=4;K<=15;K=K+1) �

real (accurate modeling of delay values, double precision (64-bit))

Real delta;

time (to store simulation time)

time A_Time_Value;

realtime (to store time in real number format)

33. Addressing Net and Register Variables MSB of a part-select of a register = leftmost array index

LSB = rightmost array index

The index of part-select must be within the range specified in declaration

If word [7:0] = 8�b00000100

word [3:0] = 4

word [5:1] = 2

word [8:1] : error

34. Constants Used for readability and maintenance

Declared with keyword parameter

Value may not be changed during simulation

35. Port Connections By order

By name

Empty port

Note: primitives by order only

36. Exercises

37. Find Syntax Error reg _a, abc$, 2_bit, myname, and;

integer [7:0] count_index;

module some_machine (y2,y1,x3,x2,x1,x0)

input x0,x1,x2,x3;

output y1,y2;

reg x0,x1;

wire x2,x3;

wire y1,y2;

� �

endmodule