Arithmetic Circuits I

Arithmetic Circuits I. Iterative Circuit. Like a hierachy, except functional blocks per bit. Adders. Great example of this type of design Design a 1-bit adder circuit, then expand to n-bit adder Look at Half adder – which is a 2-bit adder, no carry in Inputs are bits to be added

Arithmetic Circuits I

E N D

Presentation Transcript

Iterative Circuit • Like a hierachy, except functional blocks per bit

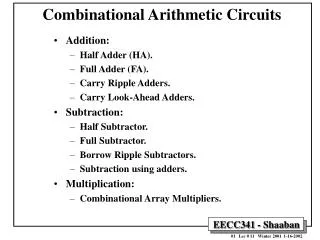

Adders • Great example of this type of design • Design a 1-bit adder circuit, then expand to n-bit adder • Look at • Half adder – which is a 2-bit adder, no carry in • Inputs are bits to be added • Outputs: result and possible carry • Full adder – includes carry in, really a 3-bit adder

Half Adder • S = X Y • C = XY

Full Adder • Three inputs. Two are operand bits, third is Cin • Two outputs: sum and carry

K Map for S • What is this?

Ripple-Carry Adder • Straightforward – connect full adders • Chain carry-out (C4) to carry-in of FA of bits A4 & B4 • C0 in case this is part of larger chain, maybe just set to zero

Carry Lookahead Adder • Note that add itself is just a 2 gate levels function • Idea is to separate carry from adder function • Then make carry approx 2-level all way across larger adder

Partial Full Adder, PFA: Inputs: A, B, C Outputs: S (sum bit), G and P Four-bit Ripple Carry Reference Adder function separated from carry

Propagate • The Pi signal is called propagate for stage i • Pi = Ai Bi • Pi high means stage i propagatesincoming carry Ci to stage i+1

What Does This Mean(Pi active) ? • No carry generated in stage i • So the propagate signal indicates that incoming carry should pass on

Generate • The Gi is generate • It’s Gi = AiBi, so new carry created • So it’s ORed with “propagated” incoming carry

Said Differently • If Ai BiAND there’s incoming carry, carry will be propagated • Si will be 0, of course • If AiBi, then a carry is generated • Incoming carry value will determine whether Si is 0 or 1

Carry Lookahead (continued) = Å = P A B G A B i i i i i i = Å = + S P C C G P C + i i i i 1 i i i • In the ripple carry adder: • Gi, Pi, and Si are local in each cell of the adder • Ci is also local in each cell • In the carry lookahead adder, in order to reduce the length of the carry chain, Ci is changed to a more global function spanning multiple cells • Defining the equations for the Full Adder in term of the Pi and Gi:

= Å = P A B G A B i i i i i i = Å = + S P C C G P C + i i i i 1 i i i Ripple Carry Delay: 8 Gates

Carry Lookahead Functions = Å = P A B G A B i i i i i i = Å = + S P C C G P C + i i i i 1 i i i C1= G0 + P0 C0 C2 = G1 + P1 C1 Substitute the expression of C1 in the equation for C2 C2 = G1 + P1 ( G0 + P0 C0 ) C2= G1 + P1 G0 + P1 P0 C0

Carry Lookahead Functions (continued) C2= G1 + P1 G0 + P1 P0 C0 For C3 C3 = G2 + P2 C2 C3 = G2 + P2 (G1 + P1 G0 + P1 P0 C0) C3= G2 + P2 G1 + P2 P1 G0 + P2 P1 P0 C0 C4= G3 + P3 G2 + P3P2 G1 + P3P2 P1 G0 + P3P2 P1 P0 C0

Carry Lookahead Functions: Summary = Å = P A B G A B i i i i i i = Å S P C i i i C1= G0 + P0 C0 C2= G1 + P1 G0 + P1 P0 C0 C3 = G2 + P2 G1 + P2 P1 G0 + P2 P1 P0 C0 C4= G3 + P3 G2 + P3P2 G1 + P3P2 P1 G0 + P3P2 P1 P0 C0

Carries Produced In Two Gate Delays* * Two gate delays after Pi and Gi in all stages are generated (one gate delay)

C2 Circuit Two Levels G1 + P1 G0 P1 P0 C0

C3 Circuit Two Levels P2 P1 G0 G2 + P2 G1 P2 P1 P0 C0

What Happens as Scale Up? • Can I realistically make 64-bit adder like this? • Have to AND 64 propagates and C0! • Compromise • Hierarchical design • More levels of gates

Remember: C4 C4= {G3 + P3 G2 + P3P2 G1 + P3P2 P1 G0} +P3P2 P1 P0 C0 C4= G0-3+P0-3C0

Making 4-Bit Adder Module • Create propagate and generate signals for whole module

Group Propagate • Make propagate of whole 4-bit block • P0-3 = P3P2P1P0

Group Generate • Make Generate of whole 4-bit block • Indicates carry generated in block

A B 4-bit adder S G P Cin Hierarchical Carry lookahead block is exercise for you A B 4-bit adder S G P Cin C4 C8 Look Ahead C0

Binary Subtraction • Example: • (19)10 – (30)10 = - (11)10 • (10011)2 - (11110)2 = - (01011)2 • We’ll use unsigned subtraction to motivate the use of • “complemented representation of signed numbers”

Example If no borrow, then result is non-negative (minuend >= subtrahend). Since there is borrow, result must be negative. The result must be corrected to a negative number.

Correcting Result of Example • What, mathematically, does it mean to borrow? • If borrowing at digit i-1 you are adding 2i

Correcting Result (continued) • If there is a borrow, M is minuend and N subtrahend, the “Difference” was 2n + M – N • What we want is magnitude of N-M with minus sign in front • Can get the magnitudeof the result (i.e. N - M ) by subtracting previous result from 2n N - M = 2n – (2n + M – N)

Algorithm to Compute M - N • Subtract N from M • If no borrow, then M N and result is OK • Otherwise, N > M get the magnitudeof the result N - M = 2n – (2n + M – N) • Add minus before the magnitude • Result is – (N-M)

Design of Subtract Ciruit • Could build a circuit to implement the previous algorithm but it will be expensive

Using 2’s & 1’s Complement Representation of Signed Numbers • People use complemented interpretation for signed numbers • 2’s complement • 1’s complement

1’s Complement • Given: binary number N with n digits • 1’s complement defined as (2n – 1) - N • Note that (2n – 1) is a number with n bits, all of them 1 • For n = 4, (2n – 1) = 1111

Example: Find 1’s Complement of N =1011001 • Notice that 1’s complement is complement of each bit

2’s Complement • Given: binary number N with n digits • 2’s complement defined as 2n – N for N 0 0 for N = 0 • Note that, since 1’s complement is(2n – 1) - N • 2’s complement is just a 1 added to 1’s complement

Important Property • Complement of a complement generates original number

New Algorithm for Computing M-N • Add 2’s complement of N to M • This is M + (2n – N) = { M – N + 2n } • If M N, will generate carry • Discard carry • Result is positive M - N • If M < N, no carry • Take 2’s complement of result • 2n - { M – N + 2n } = N-M • Place minus sign in front { - (N-M) }

Example 1 • X = 8410= 101 0100 • Y =6710= 100 0011 • X – Y = 1710 = 001 0001 • X > Y M > N; Carry generated; Discard carry; Result is positive M - N

Algorithm for Computing X - Y • Add 2’s complement of Y to X • This is X + (2n – Y) = {X – Y + 2n } • X Y, will generate carry • Discard carry • Result is positive X - Y

1710 Example 1 (continued) • X = 101 0100 minus Y = 100 0011 • 2’s comp Y = ( 011 1100 ) + 1 = 011 1101 M > N; Carry generated; Discard carry; Result is positive M - N

Example 2 • Y =6710= 100 0011 • X = 8410= 101 0100 • Y < X • Y - X = - 1710

Algorithm for Computing Y - X • Add 2’s complement of X to Y • This is Y + (2n – X) = {Y – X + 2n } • Y < X, no carry • Take 2’s complement of result • 2n - {Y – X + 2n } = X-Y • Place minus sign in front { - (X-Y) }

Example 2 (continued) • Y = 100 0011 minus X = 101 0100 • No end carry • Answer: - (2’s complement of Sum) • - 0010001 We said numbers are unsigned. What does this mean? How is -1710 represented?

Adder-Subtractor • Need only adder and complementer for input to subtract • Need selective complementer of output to make negative output from “2’s complement of Sum”