Beam diagnostics developments at LAPP: Digital part

This document presents the developments in beam diagnostics discussed at the CTF3 Collaboration Meeting on January 16, 2007. Key advancements include the design of an analog and digital front-end board for ADC acquisition, featuring a PCI acquisition board and improved sampling solutions using SAM analog memory. Highlights include memory capacity, data transmission protocols, and software integration. The meeting also addressed dosimeter readings and ongoing tests for prototypes, paving the way for future installations and enhancements in accelerator technology.

Beam diagnostics developments at LAPP: Digital part

E N D

Presentation Transcript

Beam diagnostics developments at LAPP:Digital part Louis Bellier, Richard Hermel, Yannis Karyotakis, Jean Tassan, Sébastien Vilalte CTF3 Collaboration Meeting 16-01-2007

Δ1 Analog part ADC board Σ Acquisition 4 Δ2 Near the beam <10m Front-end • Design divided in 3 parts: • Analog front-end board (4 inputs → 1 Σ and 2Δ) • Digital front-end board (sampling) • PCI acquisition board (far from radiation) CTF3 Collaboration Meeting Louis Bellier

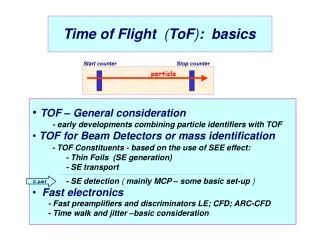

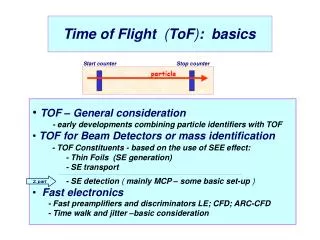

CEA SAM Memory Digital front-end • Sampling Solution: • Using the SAM analog memory. • Developed by the CEA for HESS2. • 2 memories (2x256 points) per channel • ~ we need at least 300pts during 1,5 µs • or 140 ns after CR (1 memory) • Sampling 200MSps or more. • Better delay line stability over 300MHz • Rad-Hard 200kRad • → After the SAM: ADC rad-Hard, 14 bits, 800kSps. • ↳Synchronization with the SAM output • → 35kRad technology due to FPGA CTF3 Collaboration Meeting Louis Bellier

Digital front-end principle ADC 14 Σ SAM clk1 clk clk1 ADC 14 ∆1 SAM clk1 clk1 clk ADC 14 ∆2 SAM clk1 clk1 clk FPGA clk SPECS Mezzanine board // Bus RJ 45 clk1 clk = 200MHz clk1 = 800kHz CTF3 clock Blocking CTF3 Collaboration Meeting Louis Bellier

Digital front-end board CTF3 Collaboration Meeting Louis Bellier

Acquisition The chained specs mezzanines ( ~4 at least) Digital front-end board Specs slave Ethernet cable Digital front-end board Specs slave Digital front-end board Service box Service box Specs slave Control room 100m 100m Master board 4 channels Master Board CTF3 Collaboration Meeting Louis Bellier

Specs PCI Board CTF3 Collaboration Meeting Louis Bellier

10 data sent x3x256 wait for read from specs data stored x3x256 data sampled cell written 3x256 30 41 40 60 50 send the data read analog memory sampling with ADC write in FPGA ’s ram send interruption to specs Sampling cycle waiting for blocking signal blocking pulse 20 write in analog memory CTF3 Collaboration Meeting Louis Bellier

Beam diagnostic 1 2 1 4 Gateway (Linux) SPECS Master SPECS Bus 1 1..4 3 1 Signals (Σ,Δ1,Δ2) Digital Front-end Trigger CTF3 Collaboration Meeting Louis Bellier

Disposition around the beam Analog front-end under the beam Analog signals by RJ45 (SFTP cat.6) ~5 meters Power supply and control distribution board for analog part Digital Front-end boards in crate Blocking and CTF3 clock Ethernet cable to the acquisition CTF3 Collaboration Meeting Louis Bellier

Dosimeters BPI0722 6Gy BPI0692 9Gy BPI0758 11Gy BPI0130 58Gy BPI0665 15Gy 7Gy BPI0645 45Gy BPI0622 7Gy Girder BPI0608 8Gy 7Gy Integrated dose in Gray during the last run (3weeks) CTF3 Collaboration Meeting Louis Bellier

Evolution since the last meeting • Tests and debug of the digital front-end prototype • Data transmission with the SPECS chain • Analog board configuration through SPECS and digital part • Analog memory of 512 or 1024 disable =>2 memories of 256 points on next prototype • Software development (link with FESA) • Sum channel “positive and negative” • Dosimeters around the TL1 during last commissioning • 1 prototype still in production CTF3 Collaboration Meeting Louis Bellier

Conclusion • Testing one prototype during the next run. • If digital part only after CR, just one analog memory necessary by channel. (pulse of 140ns) • First Δ in front-end and final differences (ΔV and ΔH) in software after transmission. • Software development with FESA. • Possibility to install Lapp solution on CR after conclusive results on TL2. • Installation on other part of the accelerator? CTF3 Collaboration Meeting Louis Bellier