半导体 集成电路

半导体 集成电路. 学校:湖南城市学院 院系:通信与电子工程学院 专业:电子科学与技术 时间: 2012 年上学期. 第 14 章 MOS 集成电路版图设计基础. 内容提要. IC 设计流程 版图设计规则 版图设计步骤. 总体要求. 子系统. 系统功能设计. /功能块. 寄存器传输级. 描述. 寄存器传输级. 模拟与验证. 门级逻辑. 综 合. 逻辑图. 网表. 逻辑模拟. 与验证. 电路模拟. 电路图. 与验证. 版图生成. 一、 IC 设计流程. 数字. 模拟. System C. Verilog(VHDL).

半导体 集成电路

E N D

Presentation Transcript

半导体 集成电路 学校:湖南城市学院 院系:通信与电子工程学院 专业:电子科学与技术 时间:2012年上学期

内容提要 • IC设计流程 • 版图设计规则 • 版图设计步骤

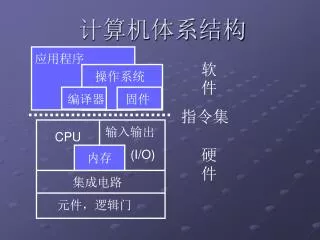

总体要求 子系统 系统功能设计 /功能块 寄存器传输级 描述 寄存器传输级 模拟与验证 门级逻辑 综 合 逻辑图 网表 逻辑模拟 与验证 电路模拟 电路图 与验证 版图生成 一、IC设计流程 数字 模拟 System C Verilog(VHDL) AHDL modelsim SPECTURE DC modelsim SPICE/ SPECTURE CADENCE的Virtuso APOLLO(自动)

版图几何设计规则和 电学规则检查 网表一致性检 查和后仿真 最终版图数据 与测试向量 制版 工艺模拟 与工艺流片 计算机辅助 ICCAT 测试( ) 生产定型 DRACULA,DIVA,CALIBRE 同右

二、IC设计规则(Design Rule) 1.宽度规则(Width rule):由工艺(光刻)极限尺寸确定 2.间距规则(space rule):避免短路

3.交叠规则(overlap rule):防止实际工艺偏差造成的开路或短路

二、IC设计规则 Cont. (以0.35umN阱CMOS工艺为例) N阱:制作PMOS管的Nwell尺寸 NW.6 Legend NW.3 Nwell NCOMP NW.2 PCOMP NW.4 NW.5

DIF.1 DIF.1 DIF.1 DIF.1 DIF.7 DIF.7 DIF.3 DIF.4 DIF.2 DIF.2 DIF.6 DIF.5 Legend N-well DIF.7c DIF.10 DIF.7c DIF.8 DIF.12 NCOMP/PCOMP:有源区 NCOMP PCOMP Poly 2 Contact

PL2.3 0.05um 0.05um PL2.5 0.1um 0.05um PL2.5 Legend N-Well Comp Poly 2 Contact PL2.6 PL2.2 PL2.4 PL2.1 PL2.3 PL2.6b PL2.6a PL2.6b PL2.6b Dog Bone 多晶硅 :

CON.2 • CON.3 Legend CON.1 CON.5 CON.6 Comp Poly 2 Contact CON.5 CON.7 CON.4 Butting Contact (Polyicide Only) 接触孔 :

Mn.3 Mn.2 Mn.4 Mn.5 Legend Metal Via/ Contact Mn.2 Vn.2 Vn.1 Mn.1 Vn.3 金属条 说明:实际版图中,顶层金属会有不同,间距和条宽都会增加。

键合点(PAD) 说明:实际版图中的pad都是有保护电路的,且厂商会提供经过若干次实验的电路。

二、版图设计步骤(人工) 版图检查与验证 总体版图 布局布线 较大的功能块 布局布线 较小的功能块 布局布线 单元库中基本单元 布图规划

1. 布图规划 根据连线最短规则将各功能模块和引脚进行整体布局 版图布局示意图: 电源环 VDD VSS cell via m2 m1 电源带

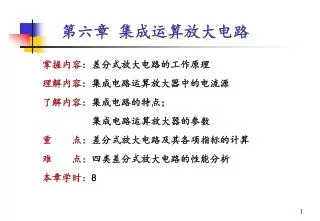

2.基本单元的设计 基本单元通常包括如反相器,传输门等在电路中需要(重复)使用的最基本的电路单元,每一层的绘制都需要仔细考虑设计规则 如:传输门加法器中的基本单元有反相器、CMOS传输门 基本单元要按照等高的原则绘制,以保证单元之间互连的兼容性,单元内部的连线采用金属1

3.功能块的设计 功能块可以根据系统的复杂程度分为多级 如:传输门加法器中的功能块可分为异或门(非)、和产生电路、进位产生电路 大部分工作是调用基本单元进行连线单元间的连线

4.PAD单元 PAD单元部分包括: (1)绑定金属线所需的可靠连接区域 (2)ESD保护结构 (4)与内部电路相连的接口 (3)输入、输出缓冲器

(2)ESD保护结构 ESD:ElectroStatic Discharge 输入I/O栅保护电路 其余ESD保护电路见P397

5.版图检查与验证 • DRC (ERC):设计规则检查 • LVS:版图与原理图一致性验证 工具自动完成,如CALIBRE,DRACULA

Ledit 版图工具简介 • 位置:桌面/tanner/ledit9/ ledit90

Ledit 窗口简介 绘图区 图形选择 鼠标各键的作用 层定义

鼠标移动精度设置: setup菜单下 design 1 Internal=0.001um

精度设置:Grid标签 1 locater=1um 最小显示精度 0.05um 鼠标移动最小距离0.05um

Intel 8486 版图与芯片示意图: 生产工艺 实际芯片 版图

P= P= 传输门加法器