VHDL 을 이용한 16 bit ALU 설계

VHDL 을 이용한 16 bit ALU 설계. Sangjin Lee. 이 상진 ( sjlee@hbt.chungbuk.ac.kr ) 충북대학교 전기전자 및 컴퓨터공학부 정보통신공학과 청주시 흥덕구 개 신동 충북대학교 학연산공동기술연구원 874 호 전화 : 043-271-2480. 2008. 4. 21. CONTENTS. ALU 의 기본 개념 16 bit ALU 구현. 1 / 5. 1. ALU 의 기본 개념. ALU (Arithmetic Logic Unit) 산술 논리 장치

VHDL 을 이용한 16 bit ALU 설계

E N D

Presentation Transcript

VHDL 을이용한 16 bit ALU 설계 SangjinLee 이 상진(sjlee@hbt.chungbuk.ac.kr) 충북대학교 전기전자 및 컴퓨터공학부 정보통신공학과청주시 흥덕구 개 신동 충북대학교 학연산공동기술연구원874호전화: 043-271-2480 2008. 4. 21.

CONTENTS • ALU 의 기본 개념 • 16 bitALU 구현 1 / 5

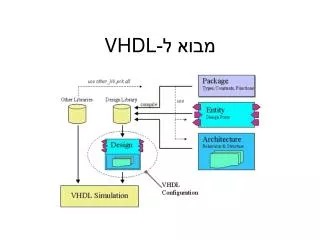

1. ALU 의 기본 개념 • ALU (Arithmetic Logic Unit) • 산술 논리장치 • Mathematician John von Neumann proposed the ALU concept in 1945, when he wrote a report on the foundations for a new computer called the EDVAC.

1. ALU 의 기본 개념 • 산술연산 회로 • 전가산기와 멀티플렉서로 이루어진 회로 • 두 개의 입력 A, B와 출력 D가 존재 • 논리연산 회로 • 게이트와 멀티플렉서로 구성 • 각 게이트가 정해진 논리 연산을 수행하고 이 결과들 중에서 하나를 멀티플렉서로 선택하여 최종 출력값을 결정

2. 16 bitALU 구현 • 동작적 표현 (process) • If 문 if sel=“0001” then result <= input_a; elsif sel=“0010” then result <= input_b; end if; • case 문 case sel is when “0001” => result <= input_a; when others => result <= x”0000”;

2. 16 bitALU 구현 • 구조적 표현 (component) • Component 문 architecture … of … is component full_adder is port( a, b : in std_logic_vector(15 downto 0); c : out std_logic; result : out std_logic_vector(15 downto 0)); end component; begin <lable> : full_adder port map( location mapping or name mapping);

감 사 합 니 다 이 상진(sjlee@hbt.chungbuk.ac.kr) 충북대학교 전기전자 및 컴퓨터공학부 정보통신공학과청주시 흥덕구 개 신동 충북대학교 학연산공동기술연구원874호전화: 043-271-2480 2008. 4. 21