第五章 VHDL 编程

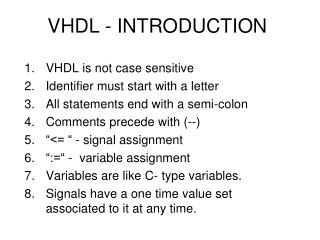

第五章 VHDL 编程. VHSIC—Very High Speed Integrated Circuit ( 1982 年) 由美国国防部 (DOD) 制定,以作为各合同商之间提交复杂电路设计文档的一种标准方案 . 1987 年被采纳为 IEEE 1076 标准 1993 年被更新为 IEEE 1164 标准. 第五章 、 VHDL 设计初步. VHDL: VHSIC Hardware Description Language. HDL 的出现是为了适应电子系统设计的日益复杂性。若以计算机软件的设计与电路设计做个类比:. 机器码好比晶体管 /MOS 管 ;.

第五章 VHDL 编程

E N D

Presentation Transcript

VHSIC—Very High Speed Integrated Circuit(1982年) 由美国国防部(DOD)制定,以作为各合同商之间提交复杂电路设计文档的一种标准方案. 1987年被采纳为IEEE 1076标准 1993年被更新为IEEE 1164标准 第五章、 VHDL设计初步

VHDL: VHSIC Hardware Description Language HDL 的出现是为了适应电子系统设计的日益复杂性。若以计算机软件的设计与电路设计做个类比: 机器码好比晶体管/MOS管; 汇编语言好比网表; HDL语言就如同高级语言。

VHDL: VHSIC Hardware Description Language 三种常用的HDL语言: 1。VHDL硬件描述语言。它适用于电路行为级、RTL级的描述,功能强,规范性好; 2。Verilog硬件描述语言。它适用于电路RTL级、门级的描述,功能强、灵活性高; 3。ABEL硬件描述语言。它也适用于电路RTL级、门级的描述,性能上比Verilog差。 VHDL和Verilog已成为IEEE标准。

VHDL: VHSIC Hardware Description Language VHDL在语法和风格上类似与现代高级编程语言。但要注意,VHDL毕竟描述的是硬件,它包含许多硬件特有的结构。是用文字化方法描述电子电路与系统。 计算机语言描述的特点是: 顺序性; HDL语言描述的特点是: 并行性。

VHDL: VHSIC Hardware Description Language VHDL的程序结构特点: 工程设计 元件、模块、系统的外部可视部分 实体 库、程序包 结构体 元件、模块、系统的内部不可视部分 实体内在功能的实现

mux21 a y ENTITYmux21IS PORT(a, b, : IN BIT ; b s S : IN BIT ; y : OUT BIT ) ; END mux21 ; VHDL: VHSIC Hardware Description Language 5.1 多路选择器的VHDL描述 例1. 2选1多路选择器的实体描述

ARCHITECTURE behave OF mux21 IS BEGIN Y <= a WHEN s=‘0’ ELSE b ; END behave; a y b S VHDL: VHSIC Hardware Description Language 结构体描述1 行为描述 S=0 S=1

d e ARCHITECTURE behave OF mux21 IS SIGNAL d, e, : BIT ;--d,e 为内部信号 BEGIN a s b y d <= a AND (NOT s); e <= b AND s ; y <= d OR e ; END behave; VHDL: VHSIC Hardware Description Language 结构体描述2 原理图描述

y = as+bs ARCHITECTURE behave OF mux21 IS BEGIN y <= (a AND (NOT s)) OR ( b AND s) ; END behave; VHDL: VHSIC Hardware Description Language 结构体描述3 布尔方程描述: 以上三种结构体描述都是并行语句

ARCHITECTURE behave OF mux21 IS BEGIN PROCESS(a,b,s) BEGIN IF s=‘0’ THEN y<=a; S=0 ELSE y<=b; a END IF; y b END PROCESS; S S=1 END behave; VHDL: VHSIC Hardware Description Language 结构体描述4 进程描述 --a,b,s 为敏感表信号

mux21仿真时序 VHDL: VHSIC Hardware Description Language 仿真结果如下:

D Q CLK LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY DFF IS PORT (CLK , D : IN_STD_LOGIC; Q : OUT_STD_LOGIC); END DEF; VHDL: VHSIC Hardware Description Language 5.2 寄存器的VHDL描述 例2 D触发器

VHDL: VHSIC Hardware Description Language ARCHITECTURE behave OF DEF IS SIGNAL Q1 : STD_LOGIC ; BEGIN PROCESS (CLK) BEGIN IF CLK’EVENTAND CLK=‘1’ THEN Q1<=D; END IF; Q <= Q1; END PROCESS; END behave;

VHDL基本结构与语法 基本构成 VHDL设计 VHDL文件 程序包(Packages) 声明在设计或实体中将用到的常数,数据类型,元件及子程序等 实体(Entities) 声明到其实体及其设计的接口,即定义本设计的输入/出端口 结构体 (Architectures) 定义了实体的实现。即电路的具体描述

VHDL文件 程序包(Packages) 声明在设计或实体中将用到的常数,数据类型,元件及子程序等 VHDL基本结构与语法 基本构成 VHDL设计

VHDL基本结构与语法: • 程序包(Package)/库(Library) 程序包定义了一组数据类型说明、常量说明、元件说明和子程序说明。以供其它多个设计实体引用。 库是专门存放预先编译好的程序包的地方,这样它们就可以在其它设计中被调用。

VHDL基本结构与语法: • 程序包(Package)/库(Library) 在VHDL语言中,数据类型、常量与子程序可以在实体说明部分和结构体部分加以说明;而且实体说明部分所定义的类型,常量及子程序在相应的结构体中是可以被使用。但是,在一个实体的说明部分与结构体部分中定义的数据类型,常量及子程序对于其它实体的说明部分与结构体部分是不可见的。

VHDL基本结构与语法: • 程序包(Package)/库(Library) 程序包/库就是为了使一组类型说明,常量说明和子程序说明对多个设计实体都成为可见的而提供的一种结构。它们如同C语言中的*.H文件,定义了一些类型说明, 函数一样。

VHDL基本结构与语法: • 程序包(Package)/库(Library) • 例: • LIBRARY ieee; • USE ieee.std_logic_1164.ALL; • USE ieee. std_logic_unsigned.ALL; • ieee是ieee标准库的标志名,两个USE语句使得以下设计可使用程序包std_logic_1164, std_logic_unsigned中预定义的内容,如std_logic,in,out的定义。

VHDL基本结构与语法: • std库,ieee库中的程序包

VHDL基本结构与语法基本构成 VHDL设计 VHDL文件 实体(Entities) 声明到其他实体及其他设计的接口,即定义本设计的输入/出端口

VHDL基本结构与语法: 实体(Entity) VHDL表达的所有设计均与实体有关,实体是设计中最基本的模块。 设计的最顶层是顶层实体。如果设计分层次,那么在顶级实体中将包含较低级别的实体。 实体中定义了该设计所需的输入/输出信号,信号的输入/输出类型被称为端口模式,同时,实体中还定义他们的数据类型。

VHDL基本结构与语法: 实体(Entity) 实体的格式如下: entity<entity_name实体名>is port <port list for your design, 列出设计的输入/输出信号端口> end<entity_name>;

VHDL基本结构与语法: 实体(Entity)例: • ENTITY cntm16 IS --实体 • PORT • (ci : IN std_logic; • nreset : IN std_logic; • clk : IN std_logic; • co : out std_logic; • qcnt : buffer std_logic_vector(3 downto 0) ); • END cntm16; 信号名 端口模式 端口类型

OUT BUFFER INOUT IN VHDL基本结构与语法: 实体:端口模式(MODE) 端口模式(MODE)有以下几种类型: IN ;OUT; BUFFER ;INOUT 端口模式可用下图说明:(黑框代表一个设计或模块)

实体:端口类型(TYPE) • 端口类型(TYPE)定义端口的数据类型,包括以下几种: • integer用作循环的指针或常数,通常不用于I/O信号,例如: • SIGNAL count :integer range 0 to 255 • count <= count + 1 • bit可取值‘0’或‘1’; • std_logic工业标准的逻辑类型,取值‘U’,‘X’,‘0’,‘1’,‘Z’, ‘W’, ‘L’, ‘H’和‘-’ --由IEEE std 1164标准定义;

VHDL基本结构与语法: 实体:端口类型(TYPE) • std_logic_vector, std_logic的组合,工业标准的逻辑类型定义总线,如: • data: in std_logic_vector(7 downto 0); • 则data表示8根数据线。 • 如给data赋值5AH可写为: • data<=“01011010”;或data<=X”5A”; X表示16进制。

VHDL基本结构与语法基本构成 VHDL设计 VHDL文件 结构体 (Architectures) 定义了实体的实现。即电路的具体描述

VHDL基本结构与语法: • 结构体(Architecture) • 所有能被仿真的实体都由一个结构体描述, 结构体描述实体的行为功能。即设计的功能,是实体中的具体逻辑。一个实体可以有多个结构体,一种结构体可能为行为描述,而另一种结构体可能为设计的结构描述或数据通道的描述。

VHDL基本结构与语法: • 结构体(Architecture) • 一个完整的、能够被综合实现的VHDL设计必须有一个实体和对应的结构体。一个实体和其对应结构体可构成一个完整的VHDL设计。一个实体可对应一个结构体或多个结构体。 • 结构体是VHDL设计中最主要部分,它一般由一些各子部分构成,如下图所示:

VHDL基本结构与语法: • 结构体(Architecture) 结构体(Architecture) 声明区(Declarations) 信号声明;声明用于该结构体的类型,常数,元件,子程序。 并发语句 信号赋值(Signal Assignments 计算结果,并赋值给信号 过程调用(Procedure Calls调用一个预先定义好的一个算法。 元件例化 (Component Instantiations) 调用另一个实体所描述的电路。即元件调用 进程(Processes) 定义一个新算法实现电路功能。在进程中赋值顺序语句。语句按放置的顺序执行。

VHDL基本结构与语法: • 结构体(Architecture)一般格式如下: • architecture<结构体名> of <实体名>is • --结构体声明区域 • --声明结构体所用的内部信号及数据类型 • --如果使用元件例化,则在此声明所用的元件 • begin --以下开始结构体,用于描述设计的功能 • --concurrent signal assignments并行语句信号赋值 • --processes 进程(顺序语句描述设计) • --component instantiations 元件例化 • end<结构体名>;

& A CO SO H_ADDER A CO & B SO B F_ADDER AIN BIN CY CIN SUM 5.3 1位二进制全加器的VHDL设计 例3、一个一位二进制全加器设计。 1、半加器 半加器逻辑原理图

A C B D H_ADDER H_ADDER CY SUM AIN E A A CO CO F BIN CIN B B SO SO F_ADDER AIN BIN CY CIN SUM VHDL基本结构与语法基本构成 2、全加器

3、VHDL语言描述 LIBRARY IEEE; --库,程序包调用 USE IEEE.STD_LOGIC_1164.ALL; ENTITY OR2 IS --实体OR2描述 PORT (A, B: IN STD_LOGIC; C::OUT STD_LOGIC); END OR2; ARCHITECTURE ART1 OF OR2 IS --结构体描述 BEGIN C<=A OR B; END ART1; A C B (1)或门

H_ADDER A CO SO B & A CO SO & B (2)半加器描述1 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY H_ADDER IS --实体H_ADDER描述 PORT (A, B; IN STD_LOGIC; CO,SO; OUT STD_LOGIC); END H_ADDER ; ARCHITECTURE ART2 OF H_ADDER IS BEGIN --结构体描述 SO<=(A OR B) AND (A NAND B); CO<=NOT(A NAND B); END ART2

ARCHITECTURE ART2a OF H_ADDER IS SIGNAL abc : std_logic_vector(1 downto 0) ; BEGIN abc <= a&b; process (abc) 相当于“then” begin case abc is when “00” => so <=‘0’ ; co<=‘0’ ; when “01” => so <=‘1’ ; co<=‘0’ ; when “10” => so <=‘1’ ; co<=‘0’ ; when “11” => so <=‘0’ ; co<=‘1’ ; when other => null ; END case; END process; END ART2a; 半加器结构体描述2

VHDL基本结构与语法: • VHDL运算符:连接运算符 • &连接,将两个对象或矢量连接成维数更大的矢量, 它可给代码书写带来方便。 • 例,为表达a=‘1’ and b=‘0’ and c=‘1’概念,可定义一个变量:vabc=a & b & c;则可用vabc=“101”表达上述内容。

ARCHITECTURE ART2b OF H_ADDER IS SIGNAL abc, cso : std_logic_vector(1 downto 0) ; BEGIN abc <= a&b; co <= cso(1) ; so <= cso(0); process (abc) 相当于“then” begin case abc is when “00” => cso <=“00” ; when “01” => cso <=“01” ; when “10” => cso <=“01” ; when “11” => cso <=“10” ; when other => null ; END case; END process; END ART2b; 半加器结构体描述3

F_ADDER AIN BIN CY CIN SUM (3)全加器 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY F_ADDER IS --实体F_ADDER描述 PORT (AIN,BIN,CIN: IN STD_LOGIC; CY,SUM: OUT STD_LOGIC); END F_ADDER; ARCHITECTURE ART3 OF F_ADDER IS COMPONENT H_ADDER --元件调用声明 PORT(A,B: IN STD_LOGIC; CO, SO: OUT_LOGIC); END COMPONENT; --半加器端口

A C B D H_ADDER H_ADDER SUM CY AIN E A A CO CO F BIN CIN B B SO SO 3、VHDL语言描述 U1 U2 U3 COMPONENT OR2 PORT(A,B: IN STD_LOGIC; C: OUT_LOGIC); END COMPONENT; SIGNAL D, E, F: STD_LOGIC; BEGIN --元件连接申明 U1: H_ADDER PORT MAP(A=>AIN, B=>BIN, CO=>D, SO=>E); U2: H_ADDER PORT MAP(A=>E, B=>CIN, CO=>F,SO=>SUM); U3: OR2 PORT MAP(A=>D, B=>F, C=>CY); END ART3;

4、说明 (1)该设计包括三个实体 OR2——2输入或非门; H-ADDER——半加器; F-ADDER——全加器。 其中:F-ADDER是顶层实体,其它两个实体(子实体)为顶层实体服务。 (2)每个实体含有:库、程序包和结构体。结构体对实体功能进行定义。

(3)实体定义的元件可以通过COMPONENT END COMPONENT 元件调用申明,PORT MAP()元件例化,信号SIGNAL的定义以及引脚连线进行元件装配。 (4)例化名u1,u2,u3的端口映射语句, A=>AIN, B=>BIN, CO=>F,SO=>SUM 表示端口名与内部信号相连及系统的外部 的端口名相连。

CNT4 4 例1、 4位加法计数器 Q ENTITY CNT4 IS CLK PORT(CLK :IN BIT; Q:BUFFERINTEGER RANG 15 DOWNTO 0); END; 注意:1、Q的端口模式为BUFFER; 2、Q的的数据类型为INTEGER。 第六章、 VHDL设计进阶 6.1 4位加法计数器的VHDL描述

1 十进制整形 35 十进制整形 10E3 十进制整形 16#D9# 十六进制整形 8#562# 八进制整形 2#11001001# 二进制整形 第六章、 VHDL设计进阶 VHDL中规定,算术操作符“+”、“-”的数据类型(除特殊说明,如重载函数的利用)只能是整形“INTEGER”。 整数的表达不加单引号。

ARCHITECTURE bhv OF CNT4 IS CNT4 BEGIN 4 Q PROCESS (CLK) CLK BEGIN IF CLK’EVENT AND CLK =‘1’ THEN Q <= Q+1 ;--Q具有I/O模式,整数类形 END IF ; END PROCESS ; END bhv ; 第六章、 VHDL设计进阶

LIBRARY IEEE; --库,程序包调用 USE IEEE..STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY CNT4 IS PORT(CLK :IN STD_LOGIC; Q:OUT STD_LOGIC_VECTOR (3 DOWNTO 0) ) ; END; 第六章、 VHDL设计进阶 例2、 4位加法计数器

ARCHITECTURE bhv OF CNT4 IS SIGNAL Q1 : STD_LOGIC_VECTOR (3 DOWNTO 0) BEGIN PROCESS (CLK) BEGIN IF CLK’EVENT AND CLK =‘1’ THEN Q1 <= Q1+1 ; END IF ; Q <=Q1 ; END PROCESS ; END bhv ; 第六章、 VHDL设计进阶

第六章、 VHDL设计进阶 注意:在算式Q1<=Q1+1中,Q1是逻辑向量STD_LOGIC_VECTOR,而所加的1是整形数,数据类型是不同的,那为何能运算呢? 原因是在实体中使用了库:USE IEEE.STD_LOGIC_UNSIGNED.ALL 该库允许对预定义的操作符“+”、“-”、“*”、“=”、“<=”、“>”、“<” 、“/=” 、“AND” 、“MOD”等,对相应的数据类型INTEGER 、STD_LOGIC和STD_LOGIC_VECTOR的操作进行了重载,通过重新定义运算符的数据类型进行操作。